Ako sa vyvíja SSD pre nadchádzajúcu dekádu

Ako je na tom vývoj polovodičových pamätí dnes a kam sa uberá? Aké strasti vývojári dnes riešia a aké technológie môžeme očakávať v tejto oblasti v najbližších piatich rokoch? A kto v tejto oblasti dominuje a bude zrejme aj naďalej dominovať?

Potešujúci pokles ceny, ktorý poslal SSD s kapacitami okolo 240 GB pod hranicu 35 eur, sa definitívne podpísal na ich súčasnej trhovej dominancii v rámci primárnych používateľských úložísk. Varianty v dnes už nevyhovujúcej kapacite 120 GB sa potopili až k 20 eurám, zatiaľ čo vhodnejšie kapacity okolo 480/500 GB začínajú už na 55 eurách a 1 TB modely na 120 eurách. V súčasnej ponuke našich najväčších e-shopov nájdete SSD disk v zruba 80 % notebookov. Väčšina naň vsádza výhradne, niektoré obsahujú do páru aj klasický HDD. Už len približne 20 % nových, na Slovensku predávaných modelov, obsahuje iba HDD s rotačnými platňami. V prípade desktopov je situácia podobná a dnes už zrejme nikto neskladá seriózny počítač, v ktorom by bol systémový disk iného typu, ako SSD. Pevné disky pravdaže nevymizli. Sú hlavným nosičom masívneho objemu serverových dát, či už v dátových centrách Googlu, Facebooku či akýchkoľvek iných firiem (v súčasnosti sa používajú HDD v kapacitách 4 až 14 TB). Zastávajú takisto rolu doplnkového veľkého dátového úložiska, či už interne alebo externe, napríklad v NAS. Z hľadiska fyzických pamätí, ktoré používatelia držia naozaj v ruke, však už polovodičové typy definitívne vládnu.

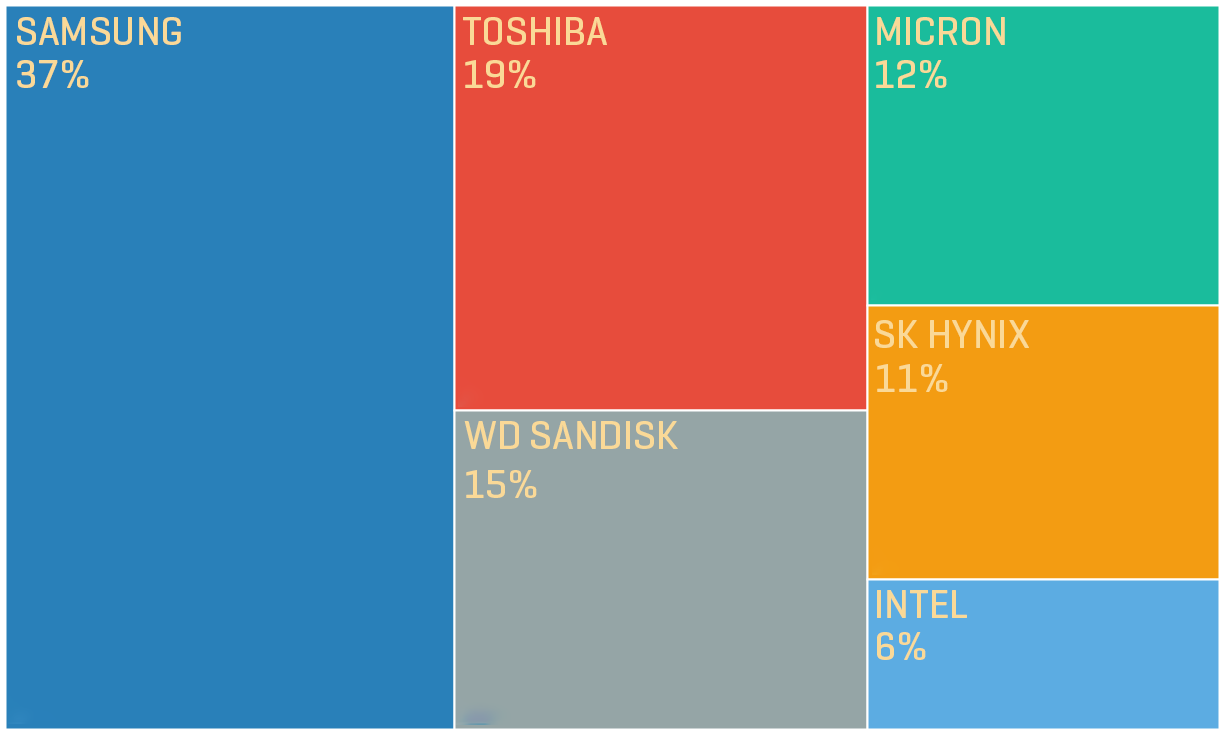

SÚČASNÍ SILNÍ HRÁČI VO VÝVOJI NAND FLASH

Jadrom technológie polovodičových úložísk je NAND flash, ktorý drží samotné dáta. Ide o špecifický typ tranzistorových pamätí, vyrábaných na kremíkových waferoch podobne ako procesory, grafické čipy a takisto operačné pamäte. Výsledkom sú pamäťové čipy, osádzané do koncových produktov, pričom v rámci notebookov a desktopov ide o SSD disky a takisto prenosné USB kľúče. V mobilnej sfére sa NAND flash čipy používajú ako interné úložisko smartfónov a tabletov a takisto vo vnútri pamäťových microSD kariet. Spôsob a kvalita výroby určuje ich vlastnosti, pričom v USB kľúčoch a pamäťových kartách sa obvykle používajú tie lacnejšie a menej rýchle modely. V SSD a smartfónoch tie rýchlejšie a výkonnejšie.

Výrobu NAND flash čipov na vrcholovej úrovni v súčasnosti zvláda už len šesť výrobcov, pričom štyria z nich dokonca vytvorili z dôvodu komplexnosti vývoja a výroby dva kooperujúce páry. V základe teda rozpoznávame len štyri rôzne vývojové prístupy. Najsilnejšiu pozíciu má v tejto oblasti už dlhodobo juhokórejský Samsung, ktorému patrí 37 % trhu, pričom prvé husle pri výrobe NAND flash hrá už viac ako jednu dekádu. Svoje NAND flash konštrukcie si vyvíja a takisto vyrába sám. Druhým najsilnejším hráčom je japonská Toshiba, z ktorej laboratórií NAND flash pôvodne vzišiel, i keď za dosť zvláštnych okolností (čomu sme sa podrobne venovali v článku Zatajené stvorenie pamätí flash: čudesný príbeh najpoužívanejšieho dátového úložiska). Aj keď je Toshiba dlhodobo druhým najsilnejším hráčom na trhu NAND flash, jej pozícia je za lídrom o polovicu slabšia a patrí jej zhruba 19 % trhu. Tretím najsilnejším hráčom je americký SanDisk, respektíve jeho vlastník Western Digital (WD), ktorý ho v roku 2016 odkúpil za 19 miliárd dolárov, v snahe zlepšiť svoju pozíciu na poli úložísk. Patrí mu 15 % trhu. Táto trojica sa spolu stará o 71 % celej NAND flash výroby. O zvyšných 29 % sa delí juhokórejský SK Hynix (11 %) a americké firmy Micron (12 %) a Intel (6 %). A to je všetko. Nech už si kúpite akýkoľvek SSD disk, smartfón, tablet, pamäťovú kartu či USB kľúč, vo vnútri nájdete NAND flash čipy jedného z týchto šiestich výrobcov. Ako sme už spomenuli, niektoré firmy pritom na vývoji spolupracujú a ich čipy sú takmer identické. Kým Samsung a SK Hynix robia vývoj a výrobu samostatne, americké firmy Micron a Intel na výrobe a vývoji spolupracujú a takisto to robí aj pár v podobe japonskej Toshiby a amerického SanDisku (WD). Nie je sa čomu čudovať. Vývoj stále lepších metód a takisto stavba masívnych produkčných liniek zásobujúcich celý svet nie je lacná záležitosť. Nároky pritom stále stúpajú. Samsung počíta na rok 2019 s nákladmi a investíciami do NAND flash na úrovni 9 miliárd dolárov (vývoj technológie a stavba fabrík a výrobných strojov). To je o 40 % viac, ako do NAND flash vložil v priebehu roku 2018 (6,4 miliardy dolárov).SÚČASNÉ METÓDY ZLEPŠOVANIA A DEFINITÍVNE ZBOHOM ZMENŠOVANIU VÝROBNÉHO PROCESU

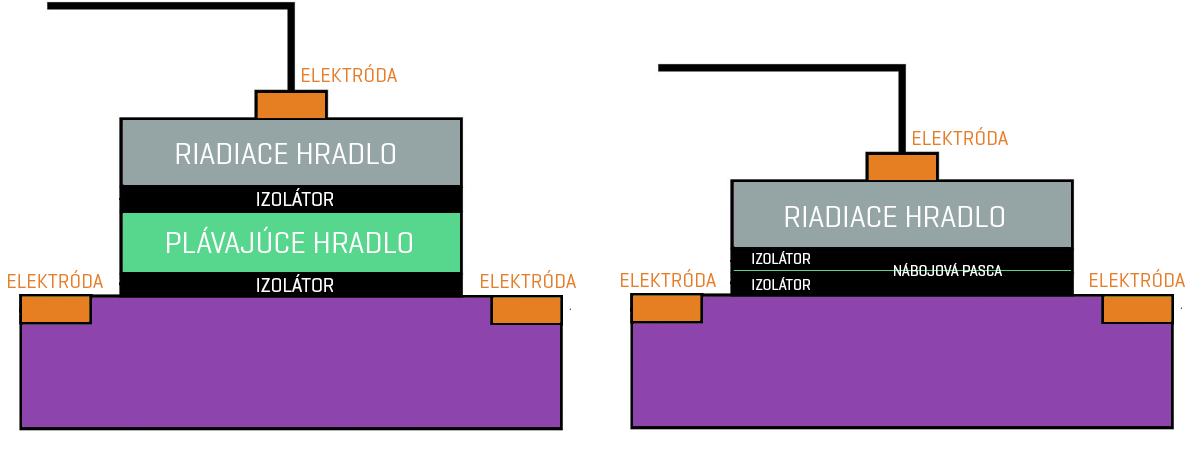

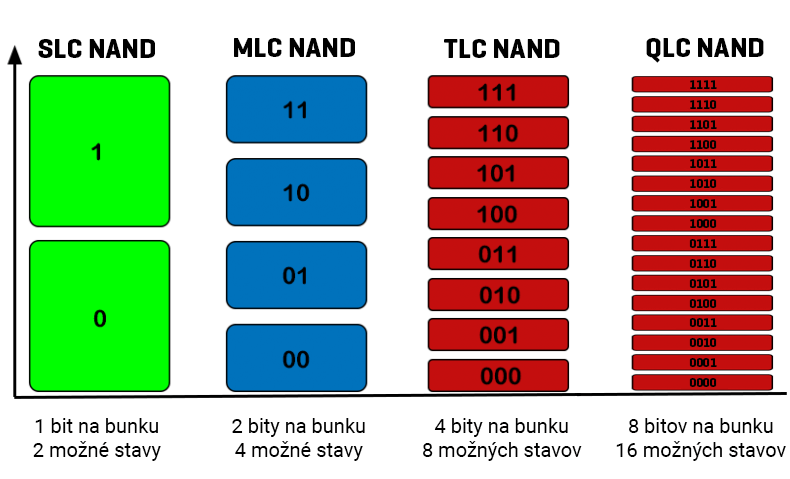

Ak vývoj NAND flash nejako prehnane nesledujete, zrejme bude pre vás prekvapením, že metóda zmenšovania výrobného procesu prestala byť v tomto odvetví schodná a zrejme nadobro skončila. Na svoju hranicu narazila pri 16/14 nm výrobnom procese v rokoch 2015 a 2016 a ďalej sa už skrátka nepohne (práve naopak urobila krok späť na 19 nm). Možno sa teraz pýtate, ako je to možné, keď pri výrobe CPU a GPU sa používajú aj 12 nm výrobné procesy a v tomto roku očakávame štart nábehu 7 nm výrobného procesu. Kľúčom k pochopeniu je to, že historicky sa pri výrobe NAND flash používali dve metódy zvýšenia dátovej hustoty. Zmenšovanie výrobného procesu (tak ako v iných odvetviach polovodičov) a vývoj riešení viacstavových pamäťových buniek. V oboch hrá hlavnú rolu tranzistor. Cieľom znižovania veľkosti výrobného procesu je vyrobiť čo najmenšie tranzistory, aby sa ich na plochu čipu zmestilo čo najviac a fungovali čoraz lepšie. V prípade CPU a GPU ide o zvyšovanie výkonu a znižovanie spotreby, v prípade dátových úložísk zase o zväčšovanie objemu uložených dát. Útok na stále menšie rozmery a tým lacnejšiu výrobu je nevyhnutný. Napríklad prechod z 25 nm procesu na 20 nm je zmenšenie o 20 %, čo znamená, že na kruhovom waferi s priemerom 300 mm môžete namiesto 371 čipov vytvoriť až 537 čipov. Ak váš konkurent prechádza na nižší výrobný proces, musíte ho nasledovať, pretože by vás zakrátko zadupal do zeme. Napríklad pri cene 3000 dolárov za wafer by ho totiž jeden čip stál približne 5 dolárov, zatiaľ čo vás až 8. Mohol by si teda dovoliť predávať rovnako veľké kapacity ako vy za nižšie ceny (čo je zriedkavé), alebo väčšie kapacity za rovnakú cenu (čo je naopak časté).

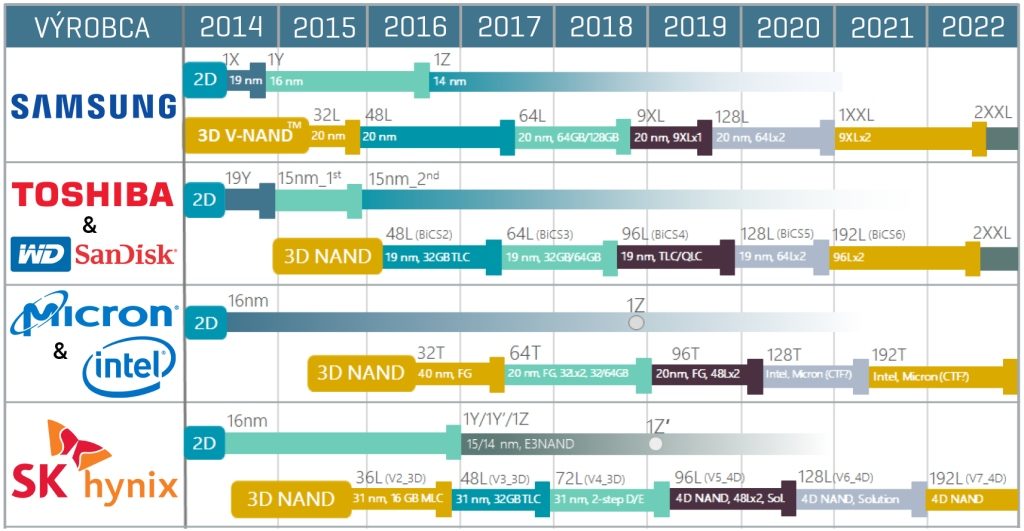

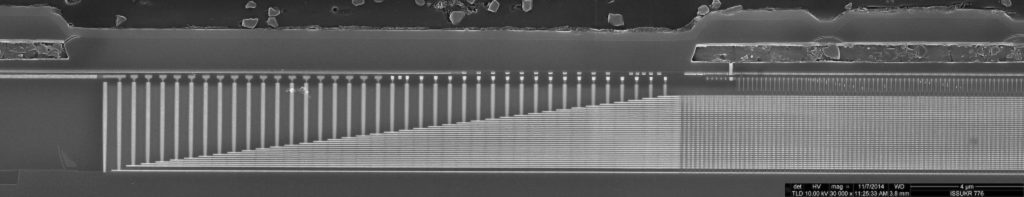

Fantastický pohľad na vertikálne NAND formou 3D modelu /ZEISS/

Z tohto dôvodu ešte pred pár rokmi hrozil seriózny koniec pokroku a vývoja NAND flash. Výrobcovia však urobili famózny a nesmierne komplikovaný krok, pri ktorom začali byť schopní litograficky vyrábať komplexné vertikálne konštrukcie. A preteky pokračujú.

ČO JE TO 3D NAND A AKO SA VLASTNE VYRÁBA?

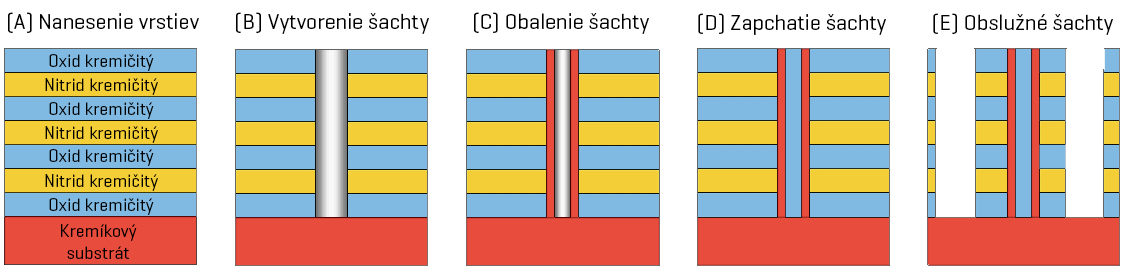

V posledných štyroch rokoch pokrok vo vývoji NAND flash prebieha formou zvyšovania počtu vertikálnych štruktúr, ktorým sme nahradili pokrok so zmenšovaním výrobného procesu. Ide o mimoriadne náročnú úlohu, ktorá si vyžiadala mnoho geniálnych riešení. V základe ide o to, že tranzistory sa nevyrábajú vodorovne na plocho, ale zvislo vo forme vedľa seba umiestnených stĺpcov. Na tomto schematickom znázornení môžete vidieť, že si nestoja „na hlavách“, ale v skutočnosti sú akoby postavené len ich pôvodné ploché štruktúry. Ide o technológiu, všeobecne označovanú ako 3D NAND, čo je trochu nešťastné. Vyvoláva to dojem, že tranzistory zmenili tvar z nejakej placky na kocku, čo nemá s realitou nič spoločné. Samotné tranzistory nie sú o nič viac 3D, než tranzistory predchádzajúcej technológie. Omnoho vhodnejšie je pomenovanie vertikálne NAND, ktoré používa Samsung (V-NAND), pretože rozdielom oproti predošlej technológii je práve zvislá konštrukcia ich reťazca. A tá je veru poriadne cenná. Ak pôvodne plochý zástup napríklad 16 tranzistorov postavíme zvislo, tak aby na waferi zaberal vlastne toľko horizontálneho miesta, ako predtým jediný tranzistor, dosiahneme objemový pokrok, ktorý sa rovná skoku z 19 nm na 5 nm výrobný proces.

VOJNA VERTIKÁLNYCH NAND FLASH JE V PLNOM PRÚDE

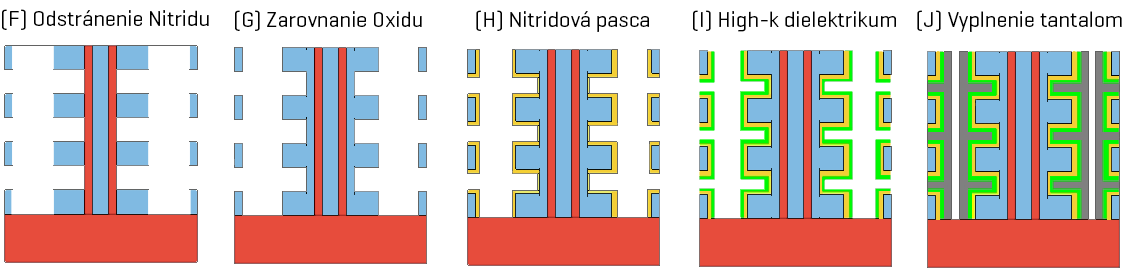

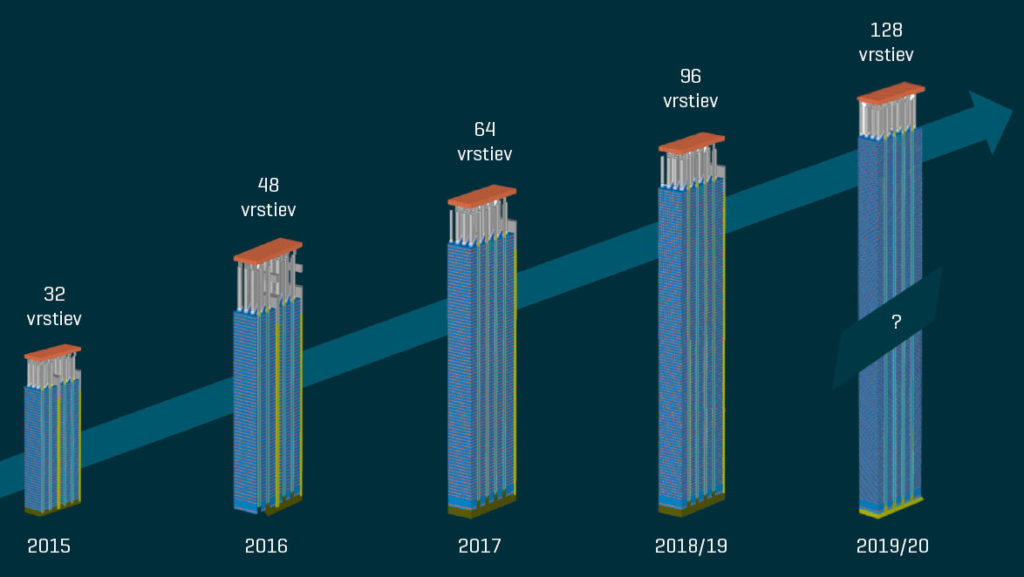

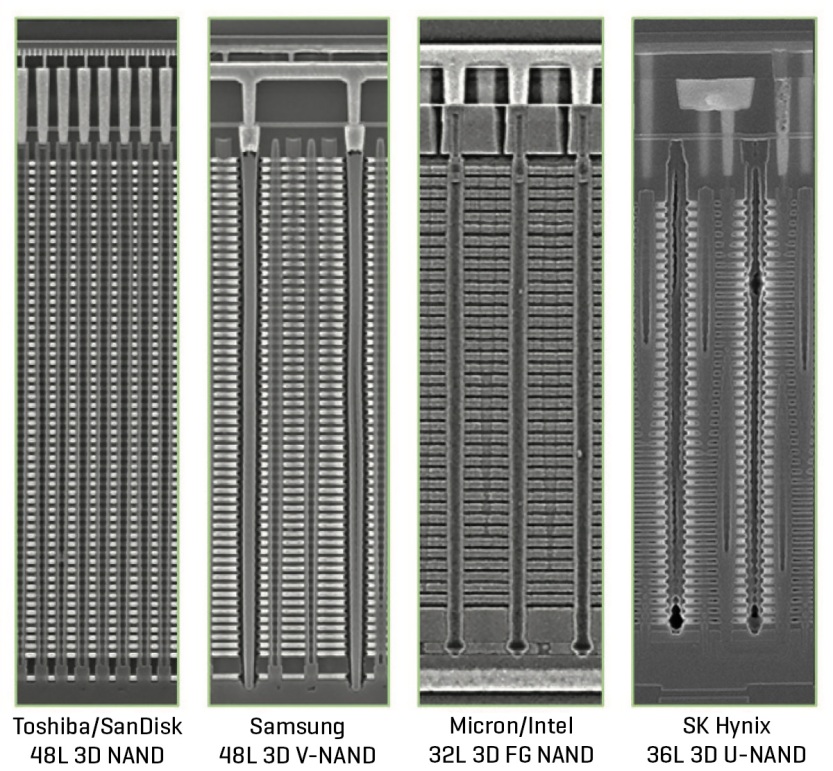

Pretek vertikálnych NAND dnes beží vysokým tempom. Tretiu generáciu v podobe prototypov so 64 vrstvami začali výrobcovia ukazovať po prvý raz na začiatku roku 2017 na medzinárodnej polovodičovej konferencii pamätí (ISSCC). Na grafe môžete vidieť, že fabriky začali tieto produkty sériovo vyrábať v lete roku 2017, pričom ako prvé začalo duo Intel/Micron, nasledované prakticky v tom istom čase duom Toshiba/SanDisk (prvý produkt na trhu tohto typu bol Intel SSD 545s). Zhruba o mesiac neskôr začali tieto produkty chrliť takisto fabriky Samsungu a počas celého roku 2018 sme sa tak mohli tešiť narastajúcej kapacite a klesajúcim cenám, ktoré 64-vrstvové vertikálne NAND priniesli do interných pamätí smartfónov či SSD diskov a ďalších produktov. Najneskôr prišiel s treťou generáciou vertikálnych NAND SK Hynix, ktorý ich začal produkovať až na sklonku roku 2017, avšak ten na rozdiel od konkurencie nepredstavil 64-vrstvové riešenie, ale 72-vrstvové.

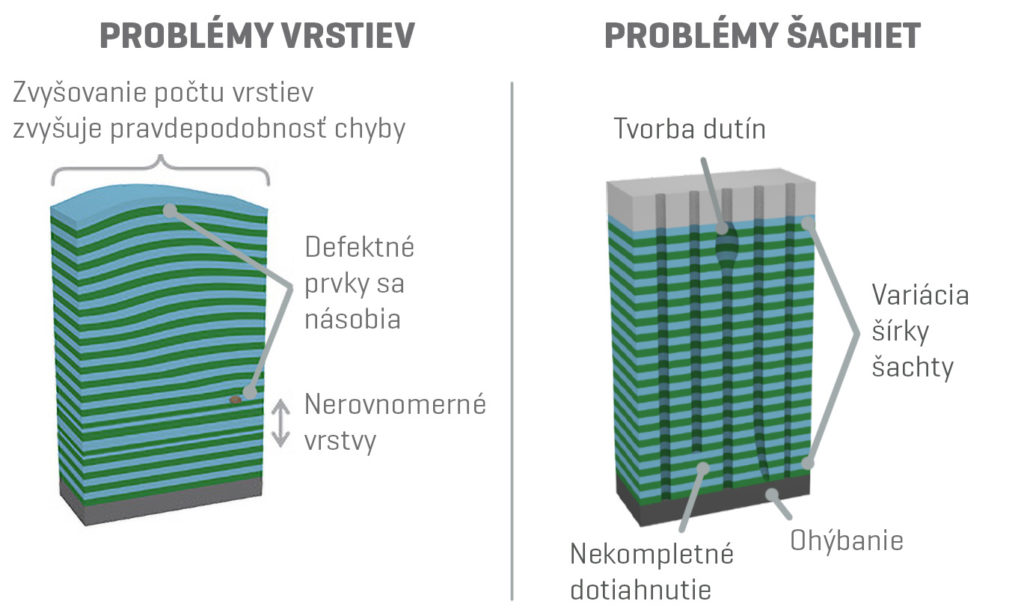

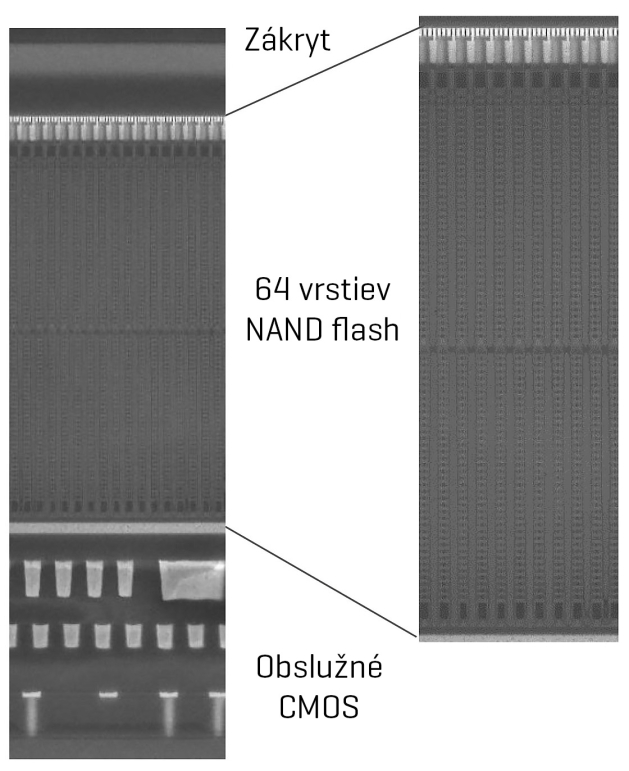

Je pritom dôležité upozorniť, že štruktúry a proces výroby jednotlivých výrobcov sa vzájomne v mnohom líšia. Ide o vrcholový vývoj, ktorí si dvaja samotári (Samsung, SK Hynix) a dva kooperujúce páry (Intel/Micron a Toshiba/SanDisk) strážia. Súčasné 64/72-vrstvové čipy NAND flash, ktoré behom roku 2018 kraľovali trhu permanentných polovodičových úložísk, sú už mimoriadne komplexná záležitosť. Vytvoriť takéto konštrukcie nie je ľahká úloha, pričom na obrázkoch môžete vidieť, že „64-poschodový“ mrakodrap je vytváraný v pároch, kde okrem 64 vrstiev tranzistorov je nutné vytvoriť aj niekoľko ďalších prvkov a vrstiev na ich ovládanie. Jeden z rozdielov, ktorým sa výrobcovia líšia je napríklad to, v koľkých krokoch sa konštrukcia „mrakodrapu“ z tranzistorov vyrába. Ako sme už popísali, na waferi sa vyrába odvrchu, teda vypaľovaním šachiet do špeciálne nanesených vrstiev na kremíkovom waferi. V súčasnosti je pomer šachiet 60 : 1, teda hĺbka šachty je 60-krát väčšia, ako jej priemer, pričom ako môžete vidieť na grafickom znázornení výroby, následne sa cez ne nanášajú rôznorodé materiály, ktoré po odleptaní vytvoria jednotlivé tranzistory. Všetko je to veľmi komplexný a na chybu náročný proces a niektorí výrobcovia si ho začali rozdeľovať na dva ľahšie kroky. Označuje sa to ako tzv. stohovanie zväzkov (string stacking), čo je v základe výroba celej mrakodrapovej konštrukcie v dvoch veľkých oddelených krokoch. Na wafer sa nanesie polovica potrebných vrstiev a vypáli sa do nich spodná polovica budúceho tranzistorového mrakodrapu. Následne sa na wafer nanesie druhá polovica vrstiev, do ktorých sa s veľkou presnosťou vypália šachty tak, aby, nadväzovali na tie spodné. Pri 64-vrstvových NAND, s ktorými sme sa stretávali v roku 2018, k takémuto postupu pristúpili duá Intel/Micron a Toshiba/Sandisk (WD) a takisto aj SK Hynix. Samsung naopak 64-vrstvové štruktúry dokázal produkovať v jednom „vrte“, kde rovno vytváral šachtu pre všetkých 64 vrstiev naraz, čo šetrí čas aj peniaze.

PROBLÉM VÝROBY PRI 128 A 256 VRSTVÁCH PRE BUDÚCE ROKY

Ako vývoj 96-vrstvových štruktúr dospel do zdarného konca a momentálne nabieha do veľkoprodukčnej fázy, začína sa zároveň aj nasledujúci pretek o 128-vrstvové riešenia piatej generácie. Niektoré analýzy predpokladajú, že prvé prototypy by sme mohli vidieť už v priebehu tohto leta. Samsung vo svojej roadmape počíta s nástupom sériovej výroby 128-vrstvových štruktúr veľmi rýchlo, a to už niekedy na jeseň. S príchodom zimy očakáva zahájenie výroby takisto aj duo Toshiba/Sandisk (WD). Micron a Intel sú zatiaľ konzervatívnejší a v roadmape so 128 vrstvami počítajú na začiatok roku 2020 a SK Hynix dokonca ešte o niečo neskôr, čo môžete vidieť na zopakovanom grafe.

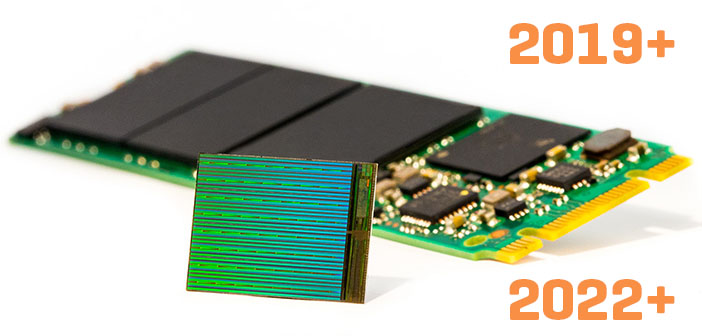

Je neisté, či sa Samsungu podarí zachovať proces výroby šachty v jednom kroku. Pri postupnom vytváraní tenučkých vrstvičiek nitridu kremičitého a oxidu kremičitého (chemickou depozíciou z plynu), je proces s nárastom vrstiev čoraz náročnejší na chybu. Vrstvy sa môžu ohýbať smerom dohora alebo dole (ako je vidieť na obrázku), čo je následne katastrofou pri vytváraní zarovnaných tranzistorov, ktoré z týchto vrstiev vzniknú. Narastá napätie a vznikajú zlomy, a teda aj chybovosť výroby. Navyše, to že sa veľký počet vrstiev podarí presne vytvoriť ešte neznamená, že do nich dokážeme vypáliť bombardovaním iónmi aj perfektnú zvislú šachtu, ktorá je stokrát taká hlboká ako široká. Často dochádza k vzniku nepresností, ako malých jaskyniek, čo môžete takisto vidieť na grafickom znázornení. Ďalšími možnými chybami je vychyľovanie šachty zo zvislej podoby, alebo jej nedopálenie až do konca. Okrem toho, čím hlbšiu šachtu potrebujeme, tým jej vypálenie iónmi trvá dlhšie. Počet Iónov ktoré dopadnú na dno sa s hĺbkou znižuje, čo môže viesť k neželaným rozdielom v šírke šachty v hornej a dolnej časti. Je obdivuhodné, že sa Samsungu podarilo proces úspešne vyvinúť aj pri 96-vrstvových štruktúrach, avšak pri 128 to bude ešte náročnejšie. Pamätajte pri tom na to, že na bežnom zhruba centimetrovom čipe je týchto šachiet niekoľko miliónov. Samsung by mohol atakovať problém tzv. kriogenickým vypaľovaním. Pri ňom sa materiál waferu pri procese bombardovania povrchu výrazne ochladzuje, čo zabraňuje mnohým neželaným reakciám a vzniku chýb. Problémom je, že kryogenické vypaľovanie si vyžaduje prítomnosť ochladzovacích plynov, obvykle tekutého dusíku, čo si vyžaduje veľkú úpravu výrobných liniek. To všetko stojí peniaze. Aj keď s kryogenickým vypaľovaním waferov sme začali experimentovať už v 80. rokoch minulého storočia, z dôvodu problémov a ceny sa nikdy vo veľkovýrobe nepoužívalo a svoje miesto hralo len vo vývoji a v experimentálnych laboratóriách. Pokrok v rámci viac ako 100 vrstvových NAND ho však môže uviesť do praxe. Nemusí sa tak ale stať. Keďže proces výroby šachty je v jednom kroku čoraz časovo dlhší a aj finančne náročnejší, Samsung možno už pri 128-vrstvových NAND bude musieť chtiac-nechtiac prejsť na stohovanie zväzkov (string stacking). Ten dnes používajú ostatní výrobcovia, ktorí nové 96-vrstvové štruktúry tvoria formou dobre zvládnutého dvojitého nanášania a vypaľovania 48 vrstiev. Lenže pri nadchádzajúcich 128 vrstvách by to znamenalo, že by museli použiť už dva 64-vrstvové kroky, pričom na dnešnom trhu 64-vrstvových štruktúr NAND flash je len Samsung, ktorý ich naozaj v jednom kroku vyrába (ostatní použili dva 32-vrstvové kroky). Obzory vrcholového výskumu sa dnes pravdaže pozerajú aj za horizont. Vo všetkých hlavných firmách prebiehajú prvé analýzy a pokusy v súvislosti s realizovateľnosťou 192-vrstvových štruktúr (optimisticky vyrobiteľné niekedy v roku 2020/2021) a napokon aj 256-vrstvových štruktúr (teoreticky v roku 2022/2023). Pri nich sa počíta, že stohovanie zväzkov (string stacking) bude už nevyhnutnosťou pre všetkých výrobcov, pričom pri 192-vrstvových štruktúrach sa zvažujú 2 až 4 zväzky a pri 256-vrstvových 4 až 8 zväzkov. Realizácia zvislej konštrukcie v štyroch či ôsmich krokoch však neprináša len negatívum v podobe zvyšovania komplexnosti, počtu krokov a teda aj ceny. Aj tu sa dostávame k technickej komplikácii toho, že kroky musia byť perfektne zarovnané, aby sa šachty (teda jednotlivé mrakodrapy tranzistorov) prepojili a na seba naviazali. Miniatúrny nanometrový posun ktorýmkoľvek smerom všetko pokazí. Kým v prípade vytvárania párového zväzku sme dnes úspešní, zväzovať takto štyri či osem častí je omnoho náročnejšie. Stačí jedna chyba a celá šachta je zničená, aj keď predchádzajúce pokusy dopadli dobre.ČUDESNÝ PROBLÉM ZVÄČŠUJÚCEHO SA SCHODISKA

Nadchádzajúce výzvy a problémy sa však netýkajú len stále hlbších šachiet. Keď sa nám bude dariť tvoriť stále vyššie vertikálne NAND konštrukcie a cez 128 vrstiev sa v nasledujúcich piatich až desiatich rokoch posunieme k 256, 512 či možno aj viac ako 1000 vrstvám, stretneme sa s veľmi zaujímavou dilemou.

Ak sa ale pozriete na prierez súčasnými štruktúrami, môžete pekne vidieť, ako na boku „mrakodrapu“ z tranzistorov postupne vystupujú jednotlivé vrstvy a sprístupňujú sa pre napojenie elektródy (vďaka tomu je možné do tranzistorov zapisovať a čítať ich). Aby túto konštrukciu bolo možné vyrobiť, musia vrstvy vytvoriť schodisko, ktoré umožní napojiť elektródu na každú novú vrstvu. Odstup vrstvičiek, a teda plocha schoda, musí byť pri tom dostatočne veľký. Problémom je, že čím väčší mrakodrap vertikálneho NAND flash firmy postavia (čím hlbšiu šachtu „vyvŕtajú“), tým väčšiu plochu zaberie nevyhnutné prístupové schodisko k jednotlivým vrstvám. Pri dnešných postupoch znamená zdvojnásobenie počtu vrstiev tranzistorov aj vodorovné zdvojnásobenie šírky schodiska. A ako sme už spomínali v úvode, horizontálne miesto na waferi je veľmi cenná komodita, ovplyvňujúca cenu. Dostávame sa teda k dileme. Vertikálne štruktúry sme začali vyrábať preto, aby sme ušetrili horizontálne miesto. Počet tranzistorov totiž stúpa do výšky, nie do šírky. Keďže je ale vertikálna konštrukcia tranzistorov stále vyššia, zvyšujú sa aj horizontálne nároky na jej obslužné štruktúry. Hrozí teda kolaps celého konceptu, pretože napr. mrakodrap s 200 vrstvami, by mohol kvôli tejto obsluhe zaberať už toľko horizontálneho miesta, ako dva mrakodrapy so 100 vrstvami. Tým pádom by prechod zo 100 na 200 vrstiev neušetril nič a zvyšovanie počtu vrstiev by už nedávalo viac zmysel. Podobá sa to na koniec pokroku v zmenšovaní výrobného procesu, ktorý kolidoval s pokrokom v tranzistoroch s viacerými stavmi. Jednou z preskúmavaných možností, ako tento problém riešiť, je sekať schodisko v dvoch rozmeroch. To ako to vyzerá, môžete vidieť na schematickom obrázku vyššie. Všimnite si, ako jeden schod oddeľuje až osem poschodí, pričom tie sa následne sprístupnia štvorstupňovým schodišťom do priečneho smeru z oboch strán. Každý priečny stupienok obsahuje dve vrstvy, pričom v jednom smere sa odhalí tá vrchná a v druhom smere hlbším odleptaním/vypálením tá spodná. Mohlo by tak dôjsť k zmenšeniu nárokov na cenný horizontálny priestor. Dnes sa však ešte nevie, či budú tieto metódy schodné, pretože cena a komplexnosť výroby rozhodne o všetkom (čo je dané nielen priestorom na waferi, ale aj počtom litografických krokov). Je isté, že rôzne firmy budú skúšať rôzne postupy, čo je v tomto odvetví bežné a úspešnejšie riešenie môže konkurencii narobiť poriadne bolenie hlavy. Takisto je treba počítať s tým, že riešenia, ktoré budú vhodné pre 128- a 192-vrstvové štruktúry, automaticky nemusia byť vhodné pri viac ako 200-vrstvových štruktúrach. Bude zaujímavé sledovať, ako sa jednotliví výrobcovia so všetkými týmito problémami v nadchádzajúcich rokoch popasujú. Nie je pravdaže nikde zaručené, že sa rýchly progres vo vývoji vertikálnych štruktúr podarí zachovať aj v nasledujúcich rokoch a naozaj sa k 256 či 512 vrstvám dostaneme. Pokojne môže nastať „veľký zásek“, aký v posledných rokoch postihol Intel, ktorý zamrzol v rámci CPU na 14 nm výrobnom procese a ten 10 nm sa mu nedarí dokončiť už niekoľko rokov. Každopádne, keď pred štyrmi rokmi pretek vertikálnych NAND flash začal, výrobcovia boli veľmi neistí, či sa im vôbec podarí prelomiť hranicu 60 vrstiev. Keďže dnes je trh plný 64-vrstvových NAND a behom tohto roku sa vychrlí aj celý zástup 96-vrstvových, vieme, že to bola planá obava. 128-vrstvové varianty sa pritom takisto zdajú na dobrej ceste. Uvidíme teda, ako to dopadne a na nové vynaliezavé inžinierske riešenia sa opäť tešíme.Podobné články

Najlepšie filmy na Netflixe 2026 (17. týždeň)

Monitory LG: extrémne rozlíšenie aj flexibilita pre hráčov

Najlepšie seriály na Netflixe 2026 (17. týždeň)

Novinka vo WhatsAppe: Zálohy správ môžu fungovať úplne inak

Mechanika alebo analóg? Klávesnica Logitech G512 X spája výhody oboch

TOP 10 filmových noviniek na internete 2026 – 17. týždeň