Ako sa meria 1 nanometrový tranzistor a čo bude menšie?

Čo vlastne vo výrobných procesoch tie čísla znamenajú? Aký veľký je tranzistor a ako malý môže byť? A kam sa pri napredovaní v zvyšovaní ich hustoty budeme v nasledujúcich dekádach posúvať?

Často krát sa v internetových komentároch a diskusiách objavuje zamyslenie IT fanúšikov nad tým, ako dlho ešte bude môcť výroba čoraz menších tranzistorov pokračovať. Nie sme už na hranici toho, ako malé tieto objekty môžu byť? Ako dlho to ešte budeme môcť robiť? Je pravdou, že vývoj čoraz lepších a pokročilejších výrobných procesov neustáva. Každý ďalší a ďalší krok je však čoraz náročnejší a zo zástupu desiatok firiem, ktoré boli schopné vrcholové výrobné procesy vyvíjať, sa zoznam skresal už len na tri. Čo ale tie čísla výrobných procesov vlastne znamenajú a ako vplývajú na rozmer a tvar tranzistoru? Čo sa myslí tým, keď sa povie, že nové AMD Ryzen procesory, alebo nové SOC v smartfónoch Huawei, Apple, Samsungu či iných firiem, sú vyrobené 7 nm výrobným procesom? A keď predtým boli vyrábané väčším a v budúcnosti budú menším, ako a čo sa to tu vlastne meria?

Nuž, na prekvapenie mnohých tento rozmer nie je veľkosťou jedného tranzistoru. Nie je to ani rozstup medzi dvoma tranzistormi a ani nejaká konkrétna časť tranzistora. Nech sa to môže zdať akokoľvek čudné, číslo ako také vlastne nevyjadruje vôbec žiadny konkrétny rozmer nejakého prvku či súčiastky, ktoré sa týmto spôsobom vyrába. Ide len o meno, ktoré sme výrobnému procesu dali. Lenže pozor! Je celkom nevhodné mať v hlave zakorenenú častú a pritom úplne chybnú predstavu, že toto číslo nemá absolútne žiadny zmysel, že ide o nejaký hlúpy marketing, či dokonca že ide o úmyselnú lož. Toto číslo nie je klamstvo. Má svoj dobrý dôvod a aj zmysel, ktorý nie je vôbec komplikované pochopiť. Poďme sa teda naň pozrieť a vysvetliť si, čo je vo veci.PREČO SA DNES VÝROBNÉ PROCESY OZNAČUJÚ POJMAMI AKO 14, 10 ČI 7 NM?

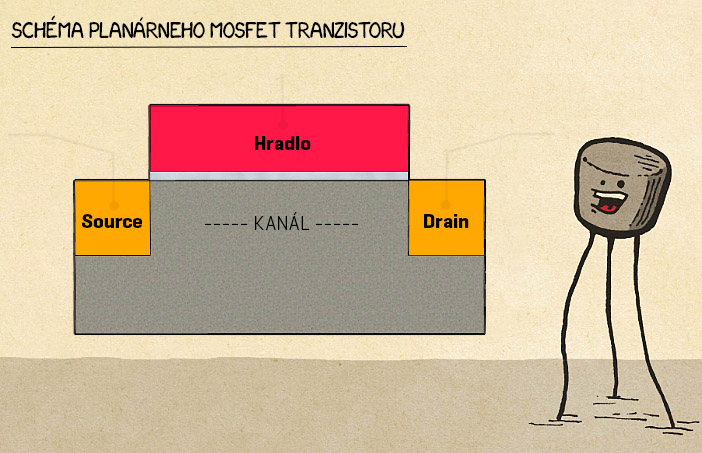

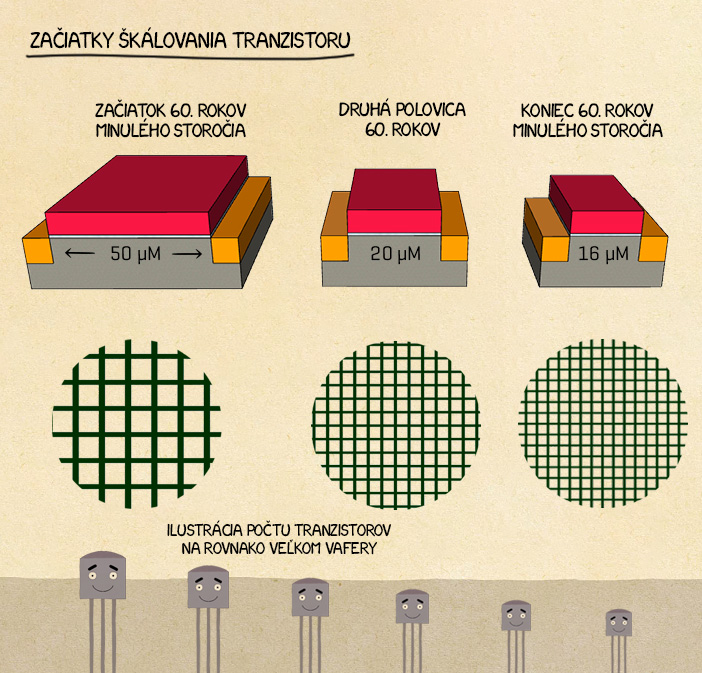

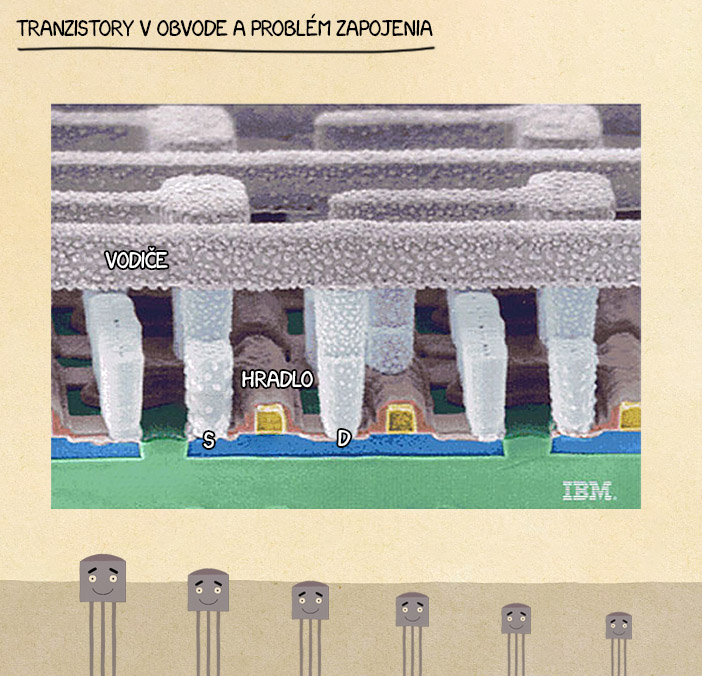

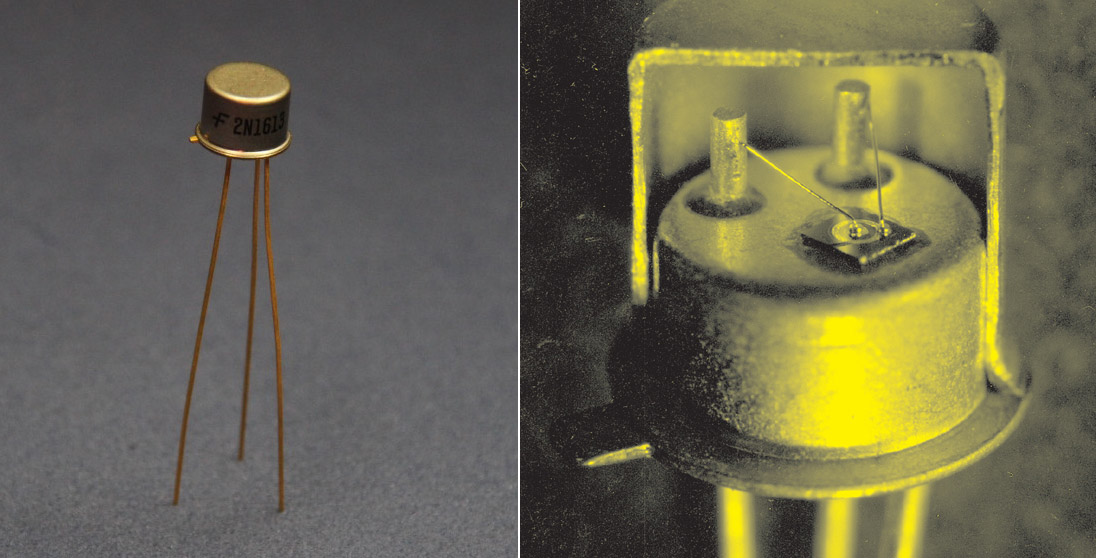

Masová produkcia kremíkových tranzistorov, ktorá započala behom 60. rokov minulého storočia, bola skutočným prielomom, ktorá naštartovala boom výpočtovej techniky. V tej dobe sa tranzistory predávali ešte po jednom kuse, pričom ich plochá kremíková platnička bola osadzovaná do ikonického hliníkového klobúčika, postaveného na troch nožičkách z kontaktov.

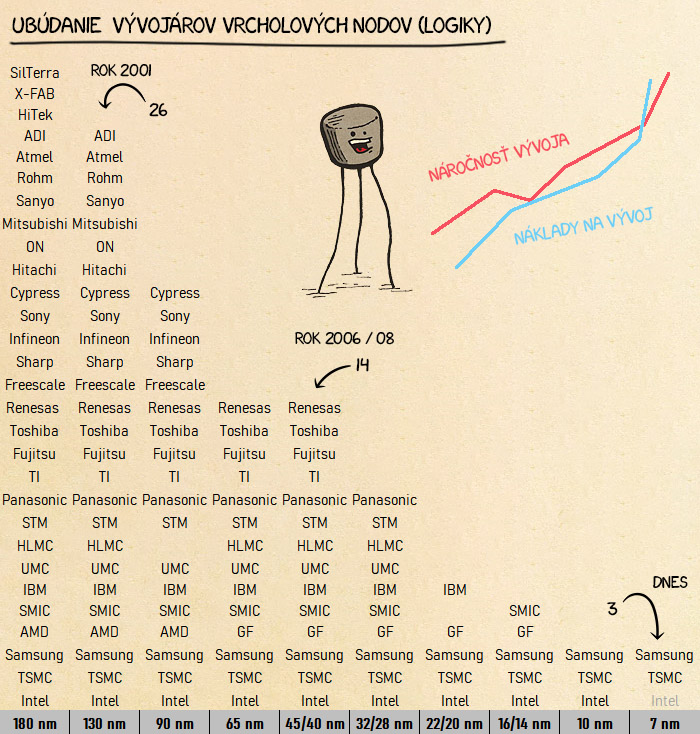

MASAKER TECHNOLOGICKEJ KOMPLEXNOSTI A JEHO PREŽIVŠÍ

Na prelome storočí, kedy sme v rokoch 1999/2000 prešli na 180 nm výrobný proces a v roku 2001/2002 na 130 nm proces, začal byť vývoj nových výrobných procesov tak technologicky náročný, že firmy, ktoré ho už nezvládli financovať, začali odpadávať ako jesenné lístie. Kým 180 nm výrobný proces zvládlo na celom svete vyvinúť 29 firiem, ten 130 nm rozbehlo už len 26 a ten 90 nm v roku 2002/2004 už len 18 (niektoré samozrejme ešte s viacročným meškaním). Stále zmenšujúce sa hradlo a približujúce sa elektródy tranzistoru prinášali nové a stále náročnejšie výzvy, v rámci ktorých začali hrať rolu dovtedy neprejavujúce sa fyzikálne javy.

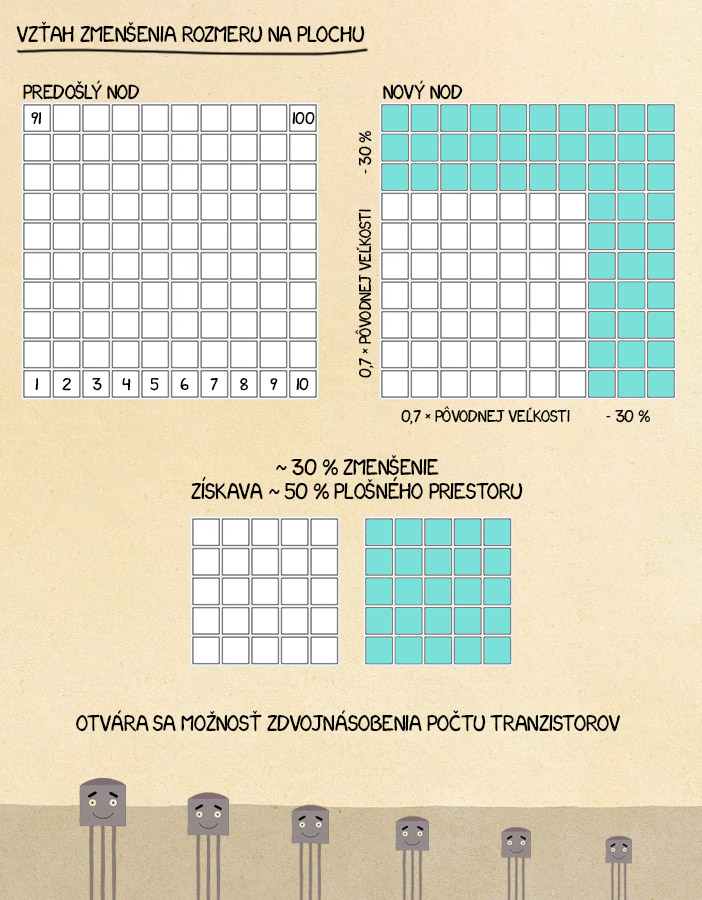

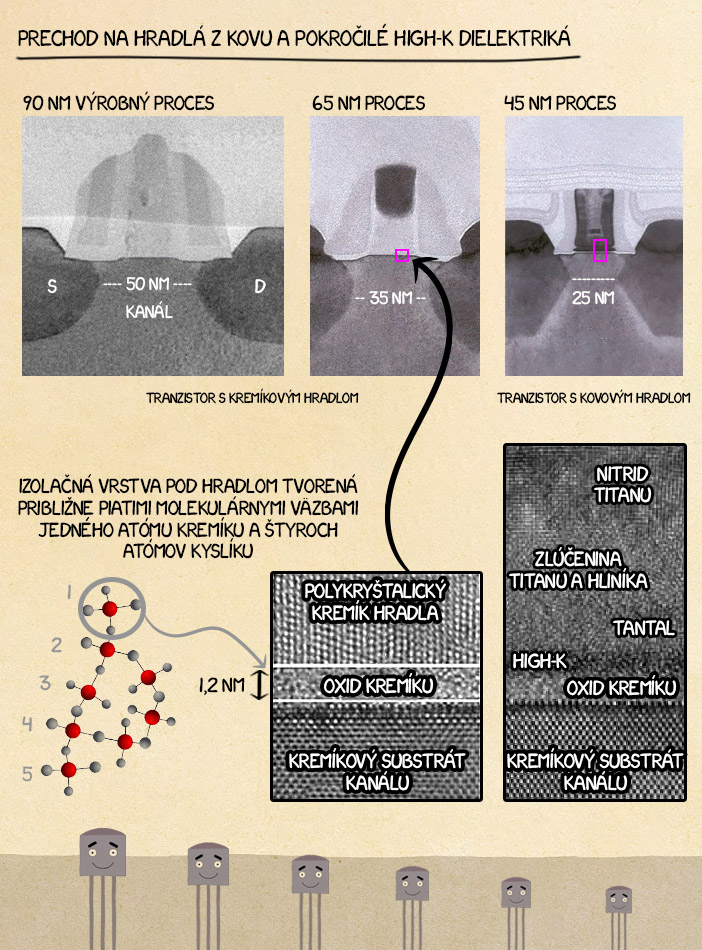

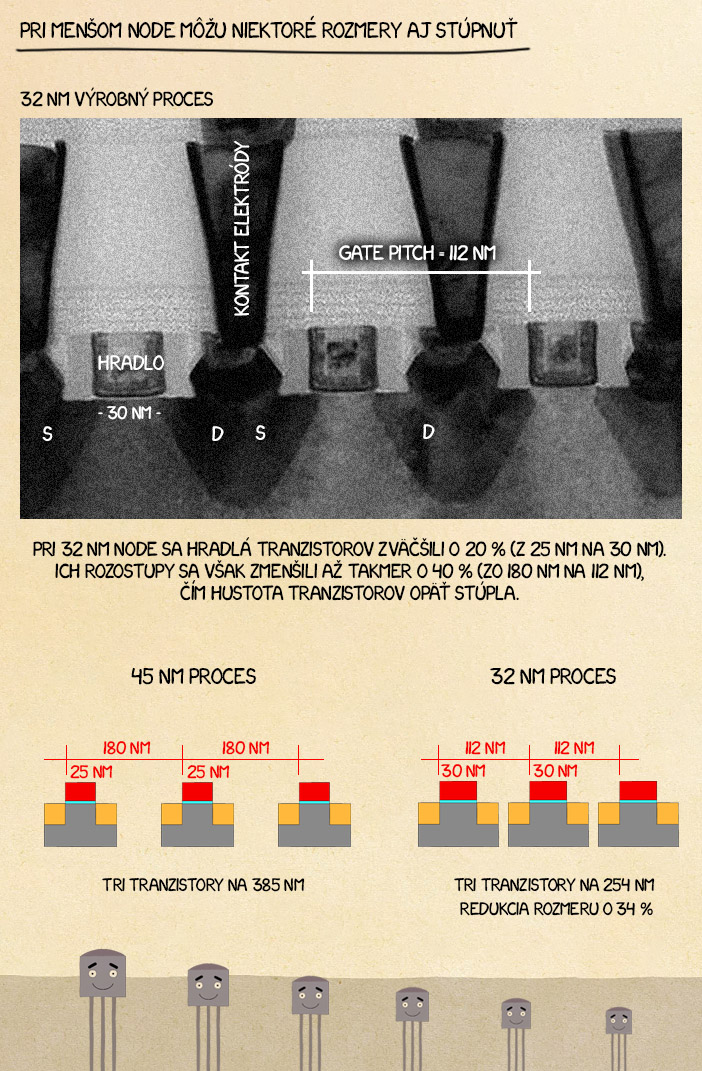

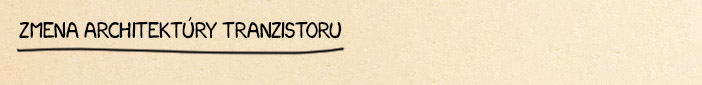

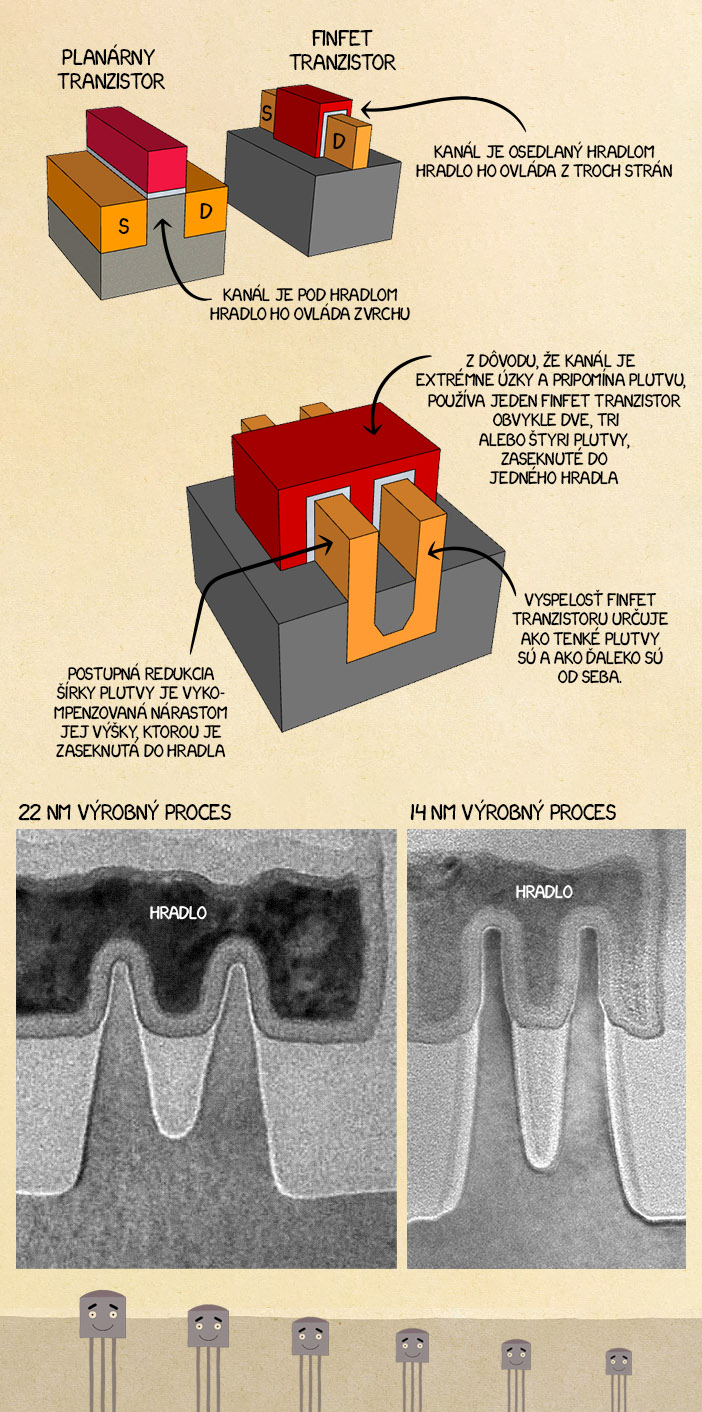

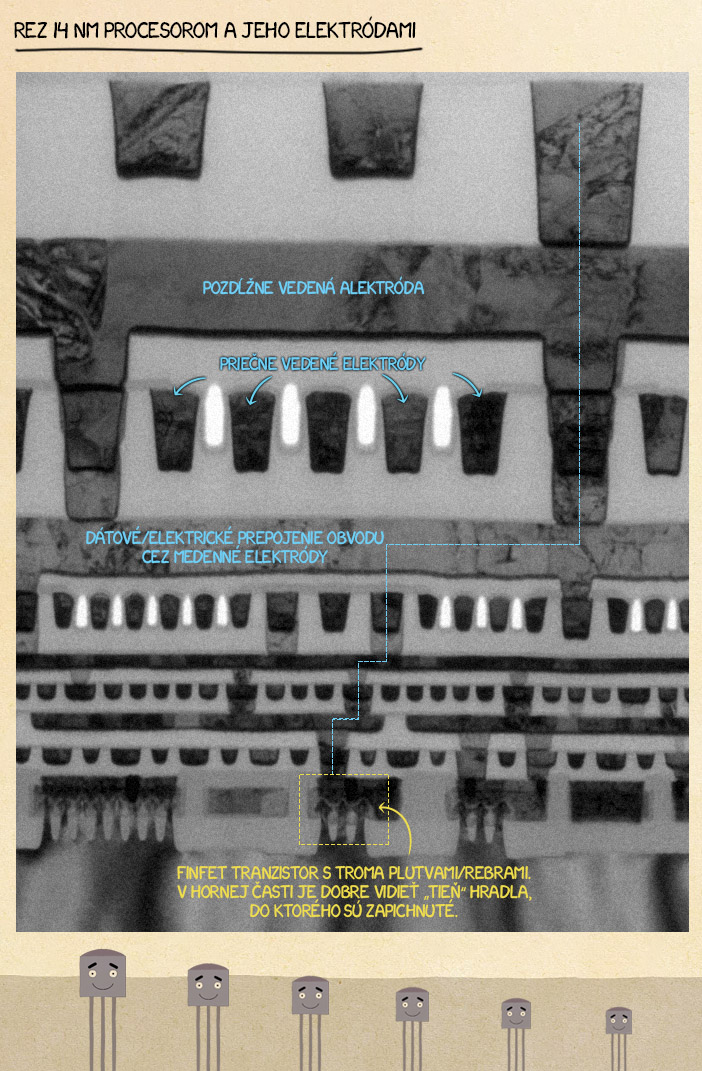

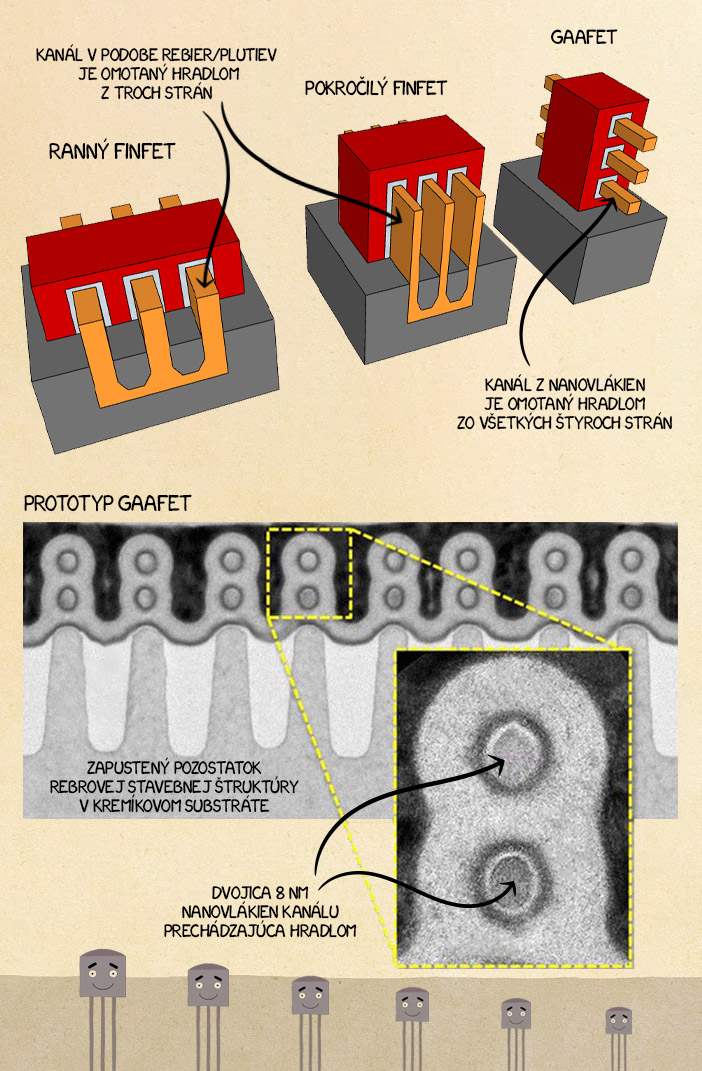

Konštrukcia tranzistoru začala narážať na prvé fundamentálne limity. Zachovanie jej funkčnosti začalo byť bojom s novými zákonmi mikroskopického sveta. Nejde pri tom o to, že by fyzika na tomto rozmere bola už iná. Ide skôr o to, že pri týchto rozmeroch začnú hrať rolu javy, ktorých efekt bol na vyšších rozmeroch zanedbateľný. Na ilustráciu tohto faktu si predstavte, ako sa v lete rozbehnete do rybníka, následkom čoho budete zakrátko po pás vo vode. Pri bližšom pohľade na hladinu ale zistíte, že rôzny malý hmyz po nej dokáže kráčať. Nie je to preto, že by preň platili iné fyzikálne zákony, ale kvôli tomu, že pri jeho rozmeroch a váhe hrá napríklad povrchové napätie vodnej hladiny významnú rolu, zatiaľ čo pri vás nulovú. Podobné je to aj v prípade čoraz menších tranzistorov. Až do 21. storočia sa vývojári mohli spoľahnúť na to, že každé ďalšie zmenšenie tranzistoru akoby automaticky prinieslo zvýšenie rýchlosti jeho práce a zníženie spotreby. Pri 90 nm výrobnom procese (rok 2002) sa však celá táto rozprávka navždy skončila. Tranzistory začali byť už také malé, že miniatúrna vzdialenosť medzi ich elektródami začala spôsobovať zvyšovanie neželaných parazitických únikov prúdu. Inak povedané, medzi elektródami začalo tiecť malé množstvo prúdu, aj v prípade že hradlo kanál „zavrelo“. Spotreba tranzistorov sa tak naopak začala prirodzene automaticky zvyšovať. Nový výrobný proces už teda prestal prinášať darček zadarmo, že všetko sa po zmenšení akoby zázrakom zlepší. Naopak sme si museli zvyknúť na to, že po zmenšení sa začne všetko zhoršovať a my s týmto zhoršením musíme náročným technologickým vývojom bojovať. Musíme hľadať nové cesty a pokročilé materiály a riešenia, ktoré nám umožňujú, aby tranzistory po zmenšení neboli horšie, ako tie predošlé. Najprv sa zdalo, že sa s tým bude dať bojovať obmedzovaním hrúbky izolačného oxidu pod hradlom tranzistora. Tým by sme čoraz menšiemu hradlu umožnili, aby po zopnutí lepšie ovládalo kanál pod sebou. Lenže to šlo len dočasne. Pri 65 nm výrobnom procese (rok 2005) už pod hradlom zostalo len 1,2 nm hrubé dielektrikum z oxidu kremičitého, čo je v prípade tohto materiálu hrúbka zhruba piatich atómových väzieb. 65 nm výrobný proces v rokoch 2005 až 2007 rozbehlo už len 14 firiem. Hustota budovania tranzistorov, ktorá sa počíta ako rozmer od začiatku hradla jedného tranzistoru, po začiatok hradla druhého (tzv. Gate Pitch) sa zmenšila na 220 nm. V nasledovnom 45 nm výrobnom procese (roky 2006 až 2008) sa tento rozostup zmenšil na 180 nm. Hradlá museli výrazne vylepšiť svoje vlastnosti s použitím nových pokročilých izolačných materiálov, predovšetkým high-k dielektrík (ako napr. wolfrám-hexafluorid). Hradlá ako také sa zároveň prestali vyrábať z kremíku (presnejšie z polykrištalického kremíku a nitridu kremíku, ktorý je na 65 nm snímku z mikroskopu vidieť ako tmavá časť „cukrovej homolky“), ktorý už pri miniatúrnych veľkostiach skrátka neposkytoval potrebné elektrické vlastnosti. Jeho miesto zastúpili rôzne zmesi kovov, predovšetkým zlúčeniny titanu. Pri 45 nm výrobnom procese v roku 2007 sa tak tvar hradla značne zmenil a namiesto cukrovej homolky dostal tvar ostrého hranolu. V rámci tohto výrobného procesu došlo k ataku na úplne minimálnu šírku hradla, ktoré sa podarilo zúžiť na 25 nanometrov. To pritom prinieslo tak veľa problémov, že firmy v nasledujúcom 32 nm výrobnom procese z roku 2009 už hradlo tranzistora radšej zväčšili o 20 % (na 30 nanometrov), nakoľko to poskytlo lepšie vlastnosti a stabilitu. Samotné zmenšenie výrobného procesu ako celku zaobstarala redukcia rozmeru a rozstupu iných častí. Gate Pich medzi dvoma tranzistormi sa totiž podarilo zmenšiť na 112 nm. Výrobný proces tohto kalibru však už zvládlo len 10 firiem na celom svete. Problémy s hradlom narastali a riešenia a nápady v súvislosti s jeho nedostatočnými rozmermi ubúdali. Vývojári si v tom čase už uvedomovali, že skôr či neskôr už bude nutná radikálna zmena architektúry tranzistoru, ktorá by umožnila v škálovaní pokračovať. Aj keď experimentálne bola už dlhodobo známa, uviesť ju do masovej výroby bol masívny krok vpred, ktorý nemal dovtedy v polovodičovej výrobe obdobu. Akútnu nutnosť tohto kroku si najviac uvedomoval Intel, ktorý sa ju rozhodol realizovať ako prvý pri 22 nm výrobnom procese. Tranzistor tak v roku 2011 výrazne architektonicky upravil tak, aby hradlo neležalo nad kanálom, ale ho obkročilo ako sedlo konský chrbát. Planárna Hoernicho schéma, ktorú sme poznali od 60. rokov minulého storočia, tak zamávala na rozlúčku. Vodivý kanál medzi source a drain elektródami prestal pripomínať riečne koryto a namiesto toho sa postavil a vystrčil ako plutva (anglicky – fin) a zarezal sa do hradla. Keďže tieto plutvy boli veľmi tenké, tranzistory obvykle používali tri či štyri. Avšak keďže ich hrúbka a rozostup bol malý, tranzistor sa mohol zmenšiť. Zmena konštrukcie pri tom odstránila problém s tým, že malý horizontálny rozmer hradla už nestačil na dobré ovládanie kanálu. Keďže hradlo už v tejto podobe kanál nekontrolovalo len z jednej strany (zvrchu), ale z troch (z vrchu a dvoch dlhých bokov), plocha vplyvu sa aj pri menšom rozmere zväčšila. Správne označenie tejto architektúry je FinFET, ktoré práve upozorňuje na to, že tranzistor tohto typu používa „plutvy“ respektíve „rebrá“, zaseknuté do hradla.Môžete sa stretnúť s tým, že sa tieto tranzistory označujú aj ako „3D“, čo reprezentuje fakt, že kanál sa z vodorovnej polohy postavil prakticky na bok a vystrčil sa zo substrátu. Takisto sa môžete stretnúť s pojmom „tri-gate“, čo zas označuje to, že hradlo obopína kanál z troch strán. Obe tieto pomenovania sú ale značne hlúpe, pretože situáciu popisujú nepresne. Jednotlivé prvky obvodu a tranzistorov totiž vždy mali mnoho „3D“ vrstiev (ako napríklad hradlo). Nejde o nákres na papieri. Rovnako výraz tri-gate rýchlo stratil zmysel, pretože sa začali vyrábať tranzistory s dvoma až piatimi kanálmi/rebrami, čím vlastne jedno hradlo obopína kanály napríklad dvakrát z troch strán či päťkrát z troch strán. Je preto vhodné preferovať výraz FinFET, ktorý sa používa v odbornej sfére. Vďaka prechodu na FinFET architektúru v roku 2011 Intel ušiel konkurenčným výrobcom o 3 až 4 roky. Ostatní sa totiž pokúsili vývojový skok na 22 nm nod urobiť ešte na pôvodnom planárnom procese, čo sa síce napokon podarilo piatim firmám (IBM, SMIC, Samsung, Global Foundries, TSMC), ale až po masívnych prieťahoch z dôvodu mimoriadne veľkých fyzikálnych a technologických problémov. Následne sa už pri skoku na 16/14 nm výrobný proces všetci rozhodli pre FinFET.

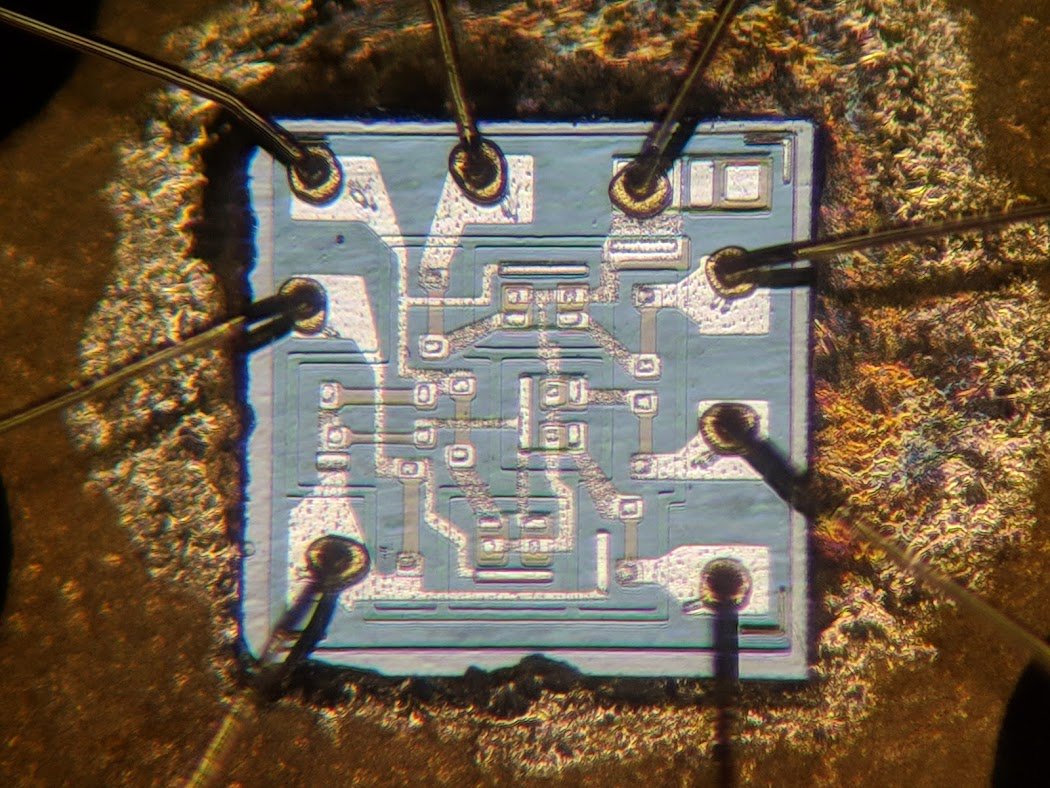

V rámci súčasného 14 nm výrobného procesu Intelu, ktorý je použitý na drvivej väčšine jeho CPU, majú rebrá (kanály) tranzistorov šírku 8 nm a výšku 42 nm. Šírka hradla cez ktoré prechádzajú je 20 nm, pričom vzdialenosť od začiatku hradla jedného tranzistoru k druhému (pitch) je 70 nm. Keďže pri 14 nm node Intel použil druhú generáciu svojho FinFET, zatiaľ čo ostatní výrobcovia svoju prvú, došlo k výraznému rozkolu pomenovávania nodov. Výrobný proces prvých FinFET tranzistorov od firiem TSMC, Samsung, Global Foundries a SMIC, označovaný ako 16 nm alebo 14 nm, bol totiž podobný, alebo mierne lepší, ako prvé FinFET tranzistory Intelu na 22 nm výrobnom procese. Druhá generácia FinFET od Intelu už bola na 14 nm výrobnom procese o príslovečný krok ďalej, čo dobre vidieť v tabuľke na obrázku nižšie. Túto konštrukciu dobehli iné firmy pri svojom ďalšom – 10 nm node. Zvládli to už ale len dve. Samsung a TSMC. Situácia sa pri tom znovu začala obracať, čo veľmi dobre demonštruje fakt, ako náročný už vývoj nových nodov je. Tretia generácia FinFET tranzistorov sa u Intelu (10 nm) dostala do masívnych vývojových problémov a ani po mnohoročných prieťahoch dnes firma nemá tento proces na takej úrovni, aby bolo na ňom ekonomicky schodné vyrábať väčšinu čipov. Do vedenia sa tak vyšvihlo v tomto smere TSMC, ktoré ekvivalentné FinFET tranzistory (v jeho prípade 7 nm výrobný proces) zvláda už hromadne vyrábať aj v rámci nemobilných výkonných CPU/GPU. Na rozdiel od Intelu, ktorý vyvíja nody a stavia výrobné fabriky polovodičov len pre použitie na vlastných čipoch, TSMC je naopak len vývojár nodov a poskytovateľ výrobných liniek. Tieto kapacity a výrobný proces si následne u neho prenajímajú výrobcovia čipov, ako napríklad AMD, Huawei, Qualcomm či Apple. Tretí výrobca vrcholových nodov, ktorým sa dnes zoznam uzaviera, je Samsung. Ten je kombináciou oboch prístupov, pričom svoj proces a fabriky využíva pre vlastné čipy, ale voľné kapacity zároveň predáva aj iným firmám a vyrába teda čipy aj pre ne (zákazník, ako napríklad Apple, sa teda môže rozhodnúť, či vyrobí svoje čipy na 7 nm výrobnom procese TSMC alebo Samsungu, podľa toho, ktorý proces sa zdá v danej dobe lepší/výhodnejší). Aktuálny 7 nm proces TSMC je súčasným vrcholom polovodičovej výroby pre čipy logiky, akými sú práve CPU či GPU (existujú aj iné procesy výroby polovodičov a to predovšetkým tie určené na výrobu pamätí. K ukážke rozdielov sa už o chvíľku dostaneme). Pri súčasnej vrcholovej výrobe TSMC je šírka rebier FinFET tranzistorov už len 6 nm, čo je o dva nanometre menej ako v predošlom node. Hradlo si zachovalo ich dobré ovládanie vďaka tomu, že ich výška stúpla zo 42 nm na 52 nm. Rozstup medzi začiatkom hradla jedného tranzistoru, po začiatok hradla druhého sa zmenšil z 66 nm na 55 nm. Možno vás napadne, že prečo výrobcovia prechod na FinFET konštrukciu tranzistorov nevyužili na to, aby nesúlad pomenovania výrobných procesov vyriešili. Keďže význam šírky hradla už nie je v rámci veľkosti tranzistoru tak smerodajný, prečo sa proces nepomenováva napríklad podľa šírky rebra? Veď predsa to má dnes pri 7 nm výrobnom procese TSMC hrúbku 6 nm, čo je dosť podobné. Nuž ale, toto rebro malo pri 10 a 14 nm výrobnom procese šírku 8 nm, takže takisto by nám to príliš užitočné nebolo. Je nutné skrátka mať na pamäti, že zmenšenia sa v rámci postupnosti nodov dosahujú rôzne a v rôznych generáciách majú na ňom podiely odlišné časti konštrukcie tranzistoru alebo obvodov. Samotný rozmer rebier, ich rozstupy či celú veľkosť tranzistorov preto nikdy nemôžeme vnímať osamostatnene. Opäť je teda dobré a žiadané, že číslovanie menších nodov pokračuje už len „virtuálne“, teda len v historickej naviazanosti a nehovorí len o konkrétnej veľkosti nejakého prvku, pretože význam jeho veľkosti sa nod od nodu mení.HOR SA NA DNO K ANGSTRÖMOM

Ako to celé bude pokračovať ďalej? Nuž, vzhľadom na to, že vrcholový vývoj nodov logiky už robia len tri firmy, môžeme len dúfať, že tomu tak zostane aspoň u nadchádzajúcich 5 nm nodov. Obzvlášť z dôvodu, že dochádza k ďalšiemu zlomu a rebrová FinFET konštrukcia tranzistoru prestáva slúžiť. Je dlhodobo známe, že pri ďalšom zmenšovaní sedlový kontakt hradla s kanálom bude čoraz viac nedostačujúci a dostaneme sa k podobnému problému, akému čelilo predtým ležaté hradlo. Úniky prúdu budú priveľké a hradlo nebude môcť dobre tranzistor zavierať.

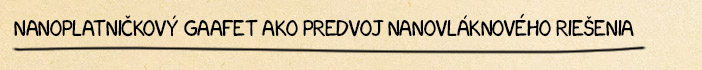

Vrcholom celého konceptu MOSFET tranzistoru je, aby hradlo kanál kompletne obkolesilo zo všetkých strán. Táto konštrukcia sa nazýva GAA-FET, čo práve tento tvar „hradlo celkom okolo“ popisuje (Gate All Around – field effect transistor). V základe sa pri tejto konštrukcii počíta s tým, že kanál má tvar vlákna, ktoré je hradlom obalené. Takáto konštrukcia je však mimoriadne náročná na výrobu a je dosť dobre možné, že prvá komerčná verzia GAA-FET použije namiesto nanovlákien horizontálne nanoplatničky. Toto riešenie na oko pôsobí kontraproduktívne, pretože jedna horizontálne uložená platnička zaberie viac miesta, ako jedno tenké priečne rebro FinFET tranzistoru. Rozdiel sa však hneď prejaví v momente, ako náhle sa pridajú ďalšie. Na rozdiel od FinFET ich totiž GAA-FET pridáva nad seba, nie vedľa seba, takže pri dvoch, troch či štyroch kanáloch prepichujúcich hradlo je ušetrenie miesta očividné. Nanoplatničkové riešenie Samsung vo svojich marketingových materiáloch označuje ako MBCFET (Multi-Bridge Channel FET), čo v preklade znamená „kanál v podobe viacnásobných mostov“, ide však len o meno, na ktoré si registroval medzinárodnú ochrannú známku, aby ho nikto iný v tejto súvislosti nemohol používať. V realite je toto riešenie pravdaže stále GAAFET tranzistorom, pretože hradlo je omotané kompletne okolo kanála, nech už má kanál akýkoľvek tvar. Nemá zmysel ho teda volať inak.

Je možné, že tieto platničkové GAAFET konštrukcie začneme vídať pri 5 nm výrobných procesoch (nielen od Samsungu, ale aj od Intelu či TSMC), pričom pri nasledujúcich menších nodoch ich začneme postupne zužovať, až napokon pri nabraní dostatku skúseností skončíme u nanovláknových riešení s kruhovým prierezom. Takisto pravdaže s troma, piatimi či viac vláknami na jeden tranzistor, pretože jedno by nedokázalo prenášať potrebné prúdy. Vzhľadom na to, že pri GAAFET konštrukcii sú vlákna umiestnené vertikálne nad sebou, je z hľadiska plošného rozmeru irelevantné, koľko ich je. V súvislosti s pokorením 5 nm výrobného procesu a prechodu smerom k 3, 2 a 1 nm sa môžeme dostať k tomu, že výrobcovia pre pomenovanie procesov začnú používať angströmy. Pri jednociferných číslach je totiž znižovanie čísla o 30 % ošemetné z hľadiska prílišného zaokrúhľovania. Nič pravdaže nebráni tomu, aby sme výrobné procesy naďalej označili názvami v podobe 3, 2 a napokon 1 nm. Avšak vzhľadom na to, že po nich už by sme následne museli prejsť k jednotkám v podobe pikometrov, dá sa predpokladať, že od tohto ustúpime. Číslovanie procesov v pikometroch totiž nedáva príliš zmysel. Pomenovania v podobe desiatich, siedmich či dvoch nanometrov sú stále plne v poriadku, nakoľko tieto rozmery v rámci rôznych prvkov tranzistorov používame a budeme používať (napríklad dnes v podobe rebra o hrúbke 6 nm a v blízkej budúcnosti v podobe vlákna s podobným prierezom). Mierka na úrovni pikometrov už však patrí atómom ako takým. Napríklad atóm kremíku má 111 pm a atóm germánia zas 211 pm. Samostatné atómy sú nám pravdaže k ničomu. Na to aby sme z nejakého materiálu niečo vyprodukovali a postavili nám jeden atóm nestačí. To je ako keby ste chceli postaviť malý dom z jednej tehly. Na druhú stranu, ak by sa v tranzistoroch jedného dňa začal vo veľkom uplanňovať 2D materiál, pozostávajúci vlastne z jednoatomárnej plachty materiálu (napr. z grafénu či perovskitu), prechod na mená s pikometrami by dával zmysel. Pre nadchádzajúcu dekádu je preto pravdepodobnejšie, že namiesto 3, 2 a 1 nm označenia vývojári nebudú čísla nodov prehnane zaokrúhľovať a použijú pri odčítaní 30 % plochy desatinné miesta. Tým sa dostávame k 5 nm (7 – 30% = 4,9), ďalej k 3,5 nm (5 – 30 % = 3,5) a následne 2,5 nm (3,5 – 30% = 2,45), pokračujúc k 1,75 nm (2,5 × 0,7 = 1,75) a napokon k 1,22 nm. Angström (desatina nanometra) je tu vhodnejší z dôvodu, že pre pomenovanie nodov nevyžaduje používanie desatinnej čiarky. Nody by tak mohli byť pomenované prehľadnejšie ako 35, 25, 18 a 13 Å. V rámci metrického systému je síce táto jednotka považovaná už za zastaranú, avšak bežne sa používa na vyjadrenie rozmeru molekúl, chemických väzieb a mikroskopických biologických štruktúr. Nič teda nebráni v jej používaní pre označenia nodov. U 5 nm a 35 Å nodov očakávame začatie uplatňovania nanoplatničkových GAAFET, ktoré pri 25 Å a 18 Å nodoch zrejme nahradia nanovláknové GAAFET riešenia. Pri 13 Å a 9 Å, teda v rámci 1 nm nodu, už bude zrejme nutné vyhrať boj o vyvinutie vertikálneho GAAFET tranzistoru s elektródami nad sebou. Vzhľadom na to, ako obrovsky náročné sú dnes ďalšie a ďalšie nody, týchto 5 nadchádzajúcich pomenovaní (5 nm, 35 Å, 25 Å, 18 Å a 13 Å) nám takmer určite vystačí nielen celú druhú dekádu 21. storočia, ale aj nemalý kus tej tretej.MUSIA SA VLASTNE VÝROBNÉ PROCESY VÔBEC TAKTO VOLAŤ?

Aj keď sa môže zdať, že čísla výrobných procesov sú akousi alfou a omegou výroby polovodičov, realita je taká, že v paralelne bežiacom vývoji nodov pre polovodičové pamäte už tieto názvy odišli do dôchodku. V tomto článku sme si prešli kompletnou históriou, dneškom a takisto blízkou a vzdialenejšou budúcnosťou vývoja tranzistorov pre konštrukciu pokročilých logických obvodov v procesoroch, grafických akcelerátoroch a podobných „výpočtových“ čipoch. Tranzistory však používame aj v pamätiach, kde nie sú zoskupované do komplexných logických obvodov, ale do prakticky uniformných sietí (každá časť plní rovnakú funkciu – ukladá bity, na rozdiel od logiky, kde každý časť čipu vykonáva niečo iné). V prípade operačných pamätí (DRAM) sa používa na uloženie bitu jeden tranzistor (na ovládanie) a jeden kondenzátor (na uloženie náboja/hodnoty). Spoločne tvoria jednu pamäťovú bunku. Vzhľadom na to, že jeden čip DRAM má dnes kapacity 4 či 8 gigabitov, v jeho útrobách je dnes niekoľko miliárd tranzistorov, podobne ako v dnešných procesoroch. Ich hustota a veľkosť je teda podobná, ako v prípade výrobných procesov logiky. Výrazy ako „14 nm“ či „7 nm“ nod pri nich však už budeme hľadať márne.

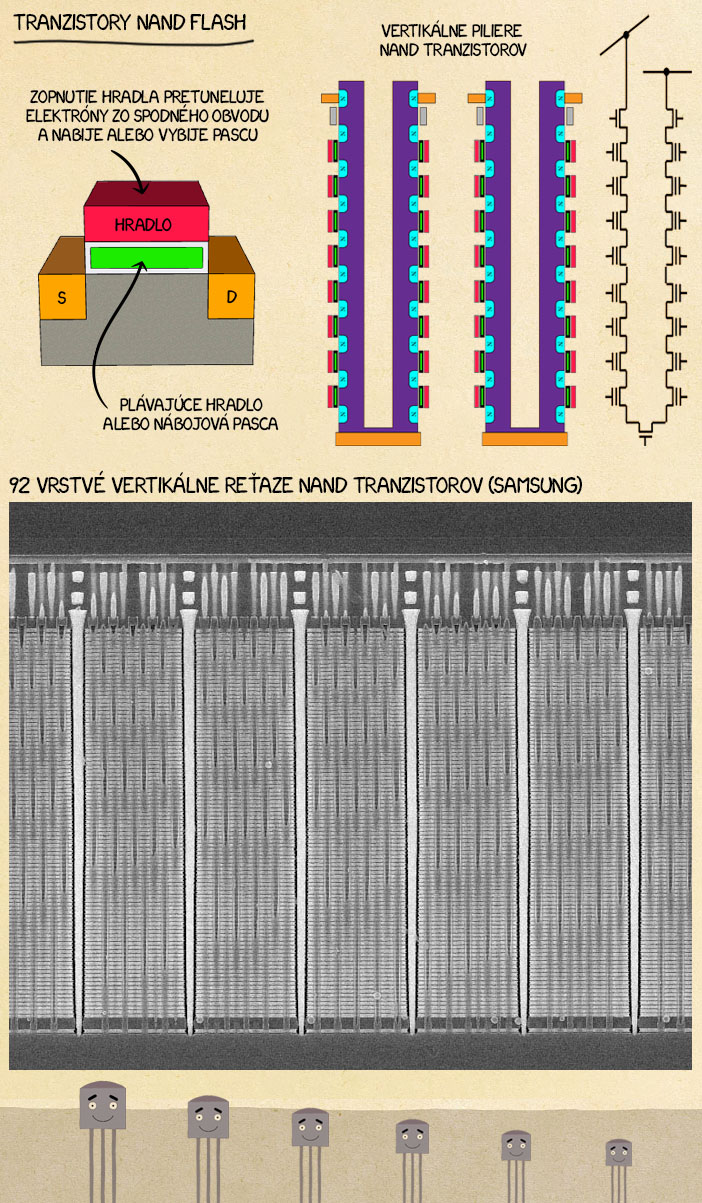

V počiatkoch polovodičového trhu sa tranzistory logiky a pamätí vyrábali prakticky na totožnom výrobnom procese, pretože tranzistory ako také sú prakticky rovnaké. Aj tu šlo v priebehu času o zmenšovanie ich planárnej konštrukcie (zmenšovaním hradla), neskôr prechod na FinFET konštrukciu a v budúcnosti ich takisto čaká prechod na GAAFET. Rozdiel tvorí to, že s tranzistorom je párovaný kondenzátor, ktorého vývoj je takisto komplexný, vďaka čomu sa cesty výrobných procesov pamätí a logiky rozišli v polovici 80. rokov minulého storočia a od vtedy postupujú samostatne. Nemožno ich teda zamieňať. Takisto ako tranzistor, aj kondenzátor sa postupne zmenšoval, ale keďže stále musel uchovávať skoro rovnako veľký elektrický náboj, pri každom zmenšení plošného rozmeru musel úbytok vykompenzovať nárastom svojej výšky. Výsledkom je, že dnes je pár kondenzátoru a tranzistoru v rámci jednej bunky prakticky rovnako plošne veľký, až na to, že kondenzátor je skoro stonásobne vyšší. Pripomína tak pilier, pod ktorým sa tranzistor krčí ako trpaslík. Tejto problematike sa podrobne venujem v samostatnom článku „Čím a kedy nahradíme RAM a Flash “, ktorý nájdete v aktuálnom vydaní nášho magazínu TOUCHIT, či už v obchodoch alebo vo svojej schránke. Vývojári výrobných procesorov operačných pamätí (DRAM), ktorých počet sa takisto skresal na vrcholovej úrovni už len na tri firmy (Samsung, SK Hynix a Micron), ešte pomerne nedávno používali na označenie svojich nodov nanometre, pričom situácia bola pomerne priamočiara. Číslo, ako napríklad v rámci 30 nm výrobného procesu DRAM, vyjadrovalo tzv. „half-pitch“, čo je polovica vzdialenosti od začiatku jedného tranzistoru (párovaného s kondenzátorom), po začiatok druhého. Je to vlastne šírka tranzistoru + medzera k druhému tranzistoru, vydelená dvoma. Pekne to tak vyjadruje dátovú hustotu, pretože záleží nielen na veľkosti tranzistora ale aj na medzere medzi tranzistormi. S preklopením na 20 a 10 nanometrovú škálu v posledných rokoch však toto názvoslovie skončilo a výrobcovia začali používať pre svoje nody pomenovania ako 2X a 2Y a v súčasnosti 1X, ktoré sa preklopia na 1Y, 1Z a zrejme aj na 1A. Kým u 2X bol ešte half-pitch jednotlivých firiem v rámci rozsahu 26 – 25 nm, v prípade 2Y už šlo 23 až 20 nm a pri súčasnom 1X o 19 až 18 nm. V prípade 1Z nodu, ktorý sa práve rozbieha, ide o 16 až 15 nm a v prípade 1A, ktorý nabehne do dvoch rokov, pôjde zrejme o half-pitch 14 až 13 nm. Ako je vidieť, upustenie od nanometrového pomenovania nodov skrátka môže existovať a časom (behom jednej až dvoch dekád) sa zrejme udeje aj v rámci výrobných procesov logiky. Je ale nutné podotknúť, že jeden z dôvodov, prečo vývojári DRAM nemali problém pôvodné názvy nodov opustiť, je to, že výrobný proces si vyvíjajú len sami pre seba a zákazníkom (výrobcom elektroniky, pamäťových modulov a podobne) predávajú len hotové čipy. Na rozdiel od výrobných procesov logiky sa teda neponúka výrobný proces ako taký, na ktorom si firmy môžu vyrábať vlastné čipy. Situácia s „dobrým a názorným menom“ je tak odlišná. Nanometrové pomenovania nodov kompletne opustil aj druhý typ polovodičovej pamäte, ktorým je NAND flash (SSD, pamäťové karty, interné úložisko smartfónov, atď.). Aj jeho výrobné procesy sú kompletne odlišné a prebiehajú samostatne. Pamäťová bunka NAND flash pamäte je tvorená čisto tranzistorom. Ide o špeciálny typ tranzistoru, ktorú je od tých bežných odlišný tým, že dokáže sám dlhodobo uchovať elektrický náboj, čo je využité na reprezentáciu binárnej hodnoty. Dokáže to vďaka tomu, že jeho súčasťou je plávajúce hradlo alebo nábojová pasca, čo je ďalší prvok, respektíve vrstvička materiálu, umiestnená medzi kanálom a hradlom Ako je vidieť na schéme nižšie, táto konštrukcia je planárna a použitie FinFET či GAAFET tu nehrá rolu, pretože hlavným limitom zmenšenia je práve veľkosť prvku, uchovávajúceho náboj. Z tohto dôvodu zmenšovanie tranzistora NAND flash skončilo v roku 2015 na 16/14 nm výrobnom procese, pričom ďalej sa už nepohlo a ani nepohne (výrobcovia sa naopak vrátili na ľahší 20 nm výrobný proces). Namiesto zmenšovania sa vývojári pustili do viacnásobného budovania zvislých tranzistorových reťazcov, v rámci ktorých sú tranzistory vytvárané nielen vedľa seba, ale aj na sebe. To je nesmierne komplexné a má vlastné špecifiká a pokiaľ vás tento vývoj zaujíma detailnejšie, nájdete ho spolu s budúcim smerom vývoja popísaný v samostatnom podrobnom článku – Ako sa vyvíja SSD pre nadchádzajúcu dekádu. Vzhľadom na to, že NAND flash tranzistor a celkový koncept obvodov zostal zamrznutý na 20 nm, číslovanie nových nodov nanometrami nedávalo už zmysel. Hustotu totiž začalo diktovať to, ako vysoké zvislé reťazce, teda mrakodrapy tranzistorov dokážeme v rámci jedného výrobného procesu vyrobiť. Jednotlivé nody NAND flash teda dnes označujeme ako 48-vrstvové (rok 2016), 64-vrstvové (rok 2017), 96-vrstvové (rok 2019) a 128-vrstvové (rok 2020). V budúcnosti pritom očakávame prechod cez 200 a dokonca aj 500 vrstiev. Zaujímavosťou je, že keby k zmene názvoslovia výrobných procesov NAND výrobcovia nepristúpili a podobne ako pri logike skrátka nanometrové číslo len ďalej virtuálne zmenšovali s nárastom hustoty, dnešné nody NAND flash by už boli hlboko pod „1 nm“ (i keď pravdaže len obrazne). Možno vás teraz napadne, že prečo takto nezačneme vrstviť aj tranzistory logiky v rámci CPU/GPU a na ich zmenšovanie sa nevykašleme. Nuž, v prvom rade, logika nie je takto uniformná. Rôzne logické časti používajú rozličné konštrukcie (podľa toho, aký čip chceme vyrobiť) a nie je teda možné vyvinúť výrobný proces, kde sa všetko podobá ako vajce vajcu, len je to menšie. Toto sa dá ale relatívne poraziť tým, že by sme vrstvili len niektoré časti, takže by tranzistory boli vedľa seba a na hlavách len v niektorých častiach obvodu. S týmto sa plánujeme popasovať zruba pri 1 nm a menších nodoch, respektíve 13, 9 či 5 angströmových nodoch, niekedy medzi rokmi 2030 a 2040. Vertikálny GAAFET s nad sebou umiestnenými elektródami je totiž potenciálne možné vrstviť a tranzistorové reťazce s ním budovať. Problémom ale je, že nikdy nebudú môcť byť príliš vysoké. Tranzistory logiky v rámci CPU a GPU sa totiž spínajú enormne rýchlo a neprestajne, čo produkuje obrovské množstvo tepla. Desiatky či dokonca stovky tranzistorov na sebe by sa tak behom okamihu upiekli ako v trúbe. Tento fakt dobre vidieť na tom, že jedna vrstva výkonnej logiky produkuje výrazne viac tepla ako akákoľvek pamäť a aj preto musíme výkonné procesory chladiť výkonnými chladičmi, zatiaľ čo čipy pamäte pri plnom výkone by sme mohli pokojne aj olizovať. Jedného dňa sa nám možno podarí vyvinúť iné mechanizmy tranzistorov či iných prvkov, ktoré masívne vrstvenie zvládnu, pričom budú produkovať pri podobnom výkone len zlomok tepla, ale zatiaľ ich nepoznáme (mrakodrapové vrstvenie nie je možné ani u pamäťových DRAM buniek, kde tomu zas bráni ozrutánsky kondenzátor, ktorý je mrakodrapom/stožiarom sám o sebe).DOBRODRUŽSTVO POKRAČUJE

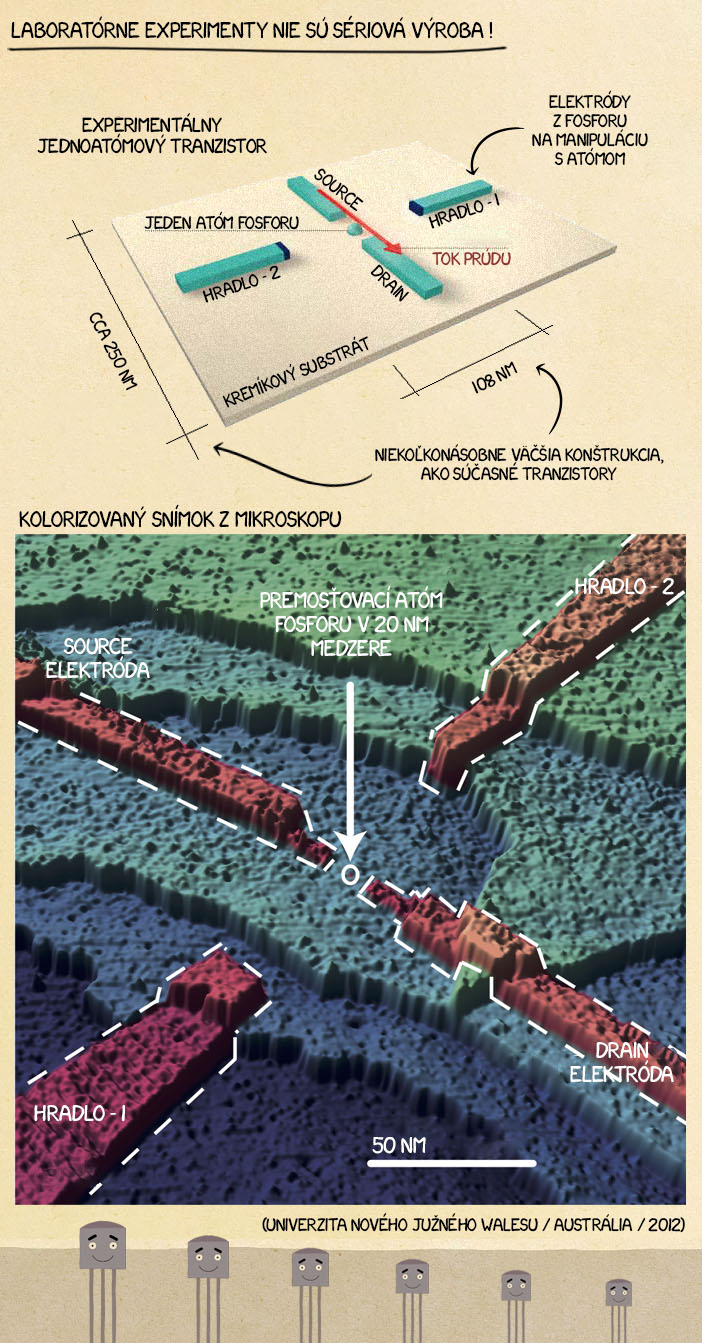

Ako je vidieť, dnes, zajtra a aj v budúcich rokoch vývoj nových nodov nekončí. Aj keď je stále náročnejší, drahší a pomalší, darí sa nám nadchádzať nové a vynaliezavé riešenia, ktoré sú neuveriteľne zaujímavé. V novo otvorených „dvadsiatych“ rokoch bude preto veľmi zaujímavé sledovať pokrok v súvislosti s vývojom nanoplatničkových a nanovláknových GAAFET. Na úplný záver ešte malé upozornenie. V bežných populárnych článkoch sa často môžete stretnúť s fantastickým reportovaním o vedeckom pokroku, kde sa s pompéznosťou oznamuje, že nejakému vedeckému tímu sa podarilo vyvinúť 1 nm, či dokonca jednoatomárny tranzistor. Na týchto správach pravdaže nie je nič zlé. Treba si ale byť vedomý toho, že fakt, že sa nejakému laboratóriu podarí vyrobiť jeden tranzistor s priemerom 1 nm, má význam z hľadiska overenia konceptu, teda toho, že vieme, že takéto veľké tranzistory sa dajú vyrobiť tak, aby fungovali. To nemá so sériovou výrobou nič spoločné. Problematike týchto správ som sa už v Nedeľníku pred nejakým časom venoval (Ako nespadnúť do čiernej diery technobludov).

Jedna vec je s obrovskými nákladmi a s obrovským vývojárskym úsilím vyrobiť v laboratóriu jediný tranzistor, ktorý sa podarí sto krát zapnúť a vypnúť (potom sa rozpadne) a vec druhá je vyvíjať komerčný nod, ktorý potrebuje za krátku dobu vyrobiť napríklad 100 miliárd funkčných tranzistorov na ploche o veľkosti jednocentovej mince, kde sú zapojené do spoločného integrovaného obvodu, pričom to celé nestojí napr. viac ako 10 eur (pretože k výrobným nákladom čipu sa priráta ešte napríklad 10 eur nákladov na zapuzdrenie, kontrolu a distribúciu, 20 eur zisku, z ktorého sa bude financovať budúci vývoj, 20 eurová marža distribútora a koncového predajcu/obchodníka a napokon 20 eur v podobe DPH štátu, aby si ho zákazník mohol kúpiť za 100 Eur). Majte to teda na pamäti. Vývoj nových a stále menších výrobných procesov tranzistorov je obrovským dobrodružstvom a napínavým súbojom, ktorý stojí za to sledovať. Len je pravdaže nutné poznať základné zákonitosti a situáciu, aby ste si všetko mohli dať do správnych súvislostí. Vďaka tomuto článku ste si okno do tohto nádherného sveta snáď pekne a príjemne pootvorili.Podobné články

Kuriózne a zábavné hardvérové bugy z celého sveta, zvládnete ich diagnostikovať?

Ako si postaviť doma procesor, veľký ako obývačka

Microsoft Káva a tajomný príbeh veľkého „pranku“ s prvkami detektívky

Koľko tranzistorov na svete existuje?

Nikolova odvážna show, ktorá naveky zmenila svet elektriky